Niente più nanometri per Intel ma una roadmap di tecnologie sempre più sofisticate

In occasione dell'evento Intel Accelerated Pat Gelsinger, CEO dell'azienda, delinea le novità future in termini di tecnologie produttive e di soluzioni di packaging, per proprii prodotti e per quello costruiti per i clienti

di Paolo Corsini pubblicata il 26 Luglio 2021, alle 23:01 nel canale ProcessoriIntel

Lo scorso mese di marzo Pat Gelsinger, CEO di Intel, ha annunciato la strategia IDM 2.0 di Intel, strutturata su 3 differenti fasi: produzione interna di chip a marchio Intel; utilizzo di fonderie di partner esterni ai quali delegare alcune delle produzioni e costituzione di Intel Foundry, entità attraverso la quale Intel opererà come foundry player nella costruzione di semiconduttori di clienti partner.

L'iniziativa nasce di fatto in parallelo con l'ingresso di Pat Gelsinger alla posizione di vertice dell'azienda americana e delinea una strategia molto chiara, che mette al centro la capacità produttiva dell'azienda al punto da renderla disponibile anche a clienti andando in questo modo a fare diretta concorrenza alle aziende produttrici di semiconduttori per conto terzi più importanti al mondo.

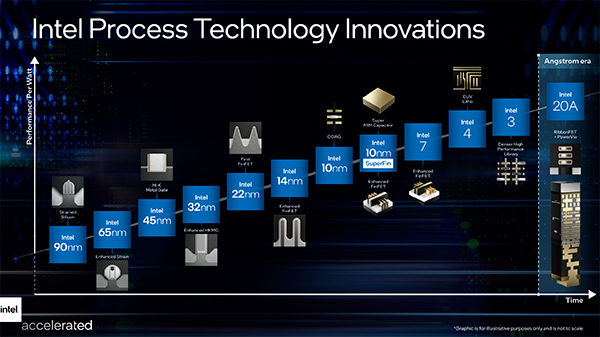

Da questo nasce per Intel una necessità, quella di poter meglio confrontare la propria tecnologia produttiva con quella dei concorrenti e in primo luogo con TSMC. I processi produttivi sono storicamente indicati servendosi di una indicazione numerica in nanometri: a valori più bassi corrisponde, in teoria, una maggiore complessità del processo produttivo. Nel corso del tempo la disponibilità di tecnologie produttive sempre più sofisticate ha visto l'utilizzo di identificatori numerici e nomenclature lontane da quello che è lo stato fisico dei chip: l'indicazione numerica in nanometri non corrisponde più da tempo alla lunghezza effettiva dei gate dei transistor. Detto in altro modo, quindi, un chip costruito con processo a 7nm di TSMC ha transistor con componenti che hanno dimensioni ben superiori a 7nm. E' ad esempio noto che a livello di densità e complessità il processo a 7nm di TSMC è di fatto equivalente a quello a 10nm FinFet che Intel utilizza al momento attuale per la produzione dei propri chip.

Da questa serie di considerazioni scaturisce la decisione di Intel di introdurre una nuova serie di nomi con i quali identificare le proprie future tecnologie produttive, scollegandosi dal concetto di nanometro. Il processo attuale, in piena produzione in volumi, è quello a 10nm di tipo SuperFin utilizzato ad esempio per i processori Core di undicesima generazione.

Il successivo passaggio sarà quello indicato con il nome di Intel 7, precedentemente indicato come Enhanced SuperFin: permetterà di ottenere un incremento delle prestazioni su consumi compreso tra il 10% e il 15% rispetto al processo 10nm SuperFin, introducendo ottimizzazione dei transistor FinFet.

Il passaggio successivo sarà al processo Intel 4, in precedenza indicato come quello a 7nm; in questo caso il miglioramento in termini di prestazioni su consumi sarà pari al 20%, facendo pieno utilizzo della litografia di tipo EUV. I processori Meteor Lake per sistemi client e i compute tile Granite Rapids per sistemi datacenter sono due dei prodotti Intel che saranno costruiti con questo processo.

A seguire troviamo Intel 3, tecnologia produttiva che promette un incremento delle prestazioni sui consumi del 18% grazie ad un incremento nell'utilizzo della EUV (Extreme Ultra Violet) e a librerie HP più dense. I primi prodotti costruiti con questa tecnologia arriveranno nelle intenzioni di Intel nel corso della seconda metà del 2023, quindi tra 2 anni.

A chiudere la roadmap ora fornita il processo Intel 20A, il primo dell'era degli angstrom (unità di misura che corrisponde a un centomilionesimo di centimetro o 0,1nm). Per questo processo Intel introdurrà significative novità, nella forma della nuova architettura di transistor RibbonFET e nella tecnologia PowerVia per le interconnessioni.

RibbonFET, l'implementazione di Intel di un transistor con gate su tutti i lati, sarà la prima nuova architettura di transistor dell'azienda da quando ha introdotto FinFET nel 2011. Questa tecnologia offre velocità di commutazione dei transistor più elevate a parità di corrente di azionamento rispetto a chip con molteplici alette, ma con un ingombro più ridotto. PowerVia è lesclusiva implementazione di Intel di alimentazione dal retro, che ottimizza la trasmissione del segnale eliminando la necessità far passare l'alimentazione al lato anteriore del wafer.

Dal 2025 Intel prevede di introdurre nuovi processi, il primo dei quali prenderà il nome di Intel 18A che in questo momento è in fase di sviluppo. Non solo tecnologie produttive ma anche tecniche di packaging per i futuri chip Intel, prodotti tanto per propri prodotti come per i clienti attraverso Intel Foundry Services.

EMIB, embedded multi-die interconnect bridge, è la prima soluzione di bridge embedded 2.5D adottata da Intel, con prodotti in produzione dal 2017. Sapphire Rapids sarà il primo prodotto per datacenter Xeon a essere commercializzato in massa con EMIB. Sarà anche il primo dispositivo a doppio reticolo nel settore, offrendo quasi le stesse prestazioni di un design monolitico. Oltre a Sapphire Rapids, la prossima generazione di EMIB passerà da un bump pitch di 55 micron a 45 micron.

Foveros sfrutta le capacità di packaging a livello di wafer per fornire una soluzione di 3D stacking unica nel suo genere. Meteor Lake sarà l'implementazione di seconda generazione di Foveros in un prodotto client e presenta un bump pitch di 36 micron, tile che coprono molteplici nodi tecnologici e una gamma di potenza termica da 5 a 125 W.

Foveros Omni inaugura la nuova generazione della tecnologia Foveros fornendo flessibilità illimitata con la tecnologia di 3D stacking ad alte prestazioni per interconnessione die-to-die e prodotti modulari. Foveros Omni consente la disaggregazione degli stampi, mescolando molteplici tile superiori con molteplici tile di base su nodi fab misti, e si stima essere pronto per la produzione di massa nel 2023.

Foveros Direct passa all'unione diretta rame-rame per interconnessioni a bassa resistenza e rende più labile il confine tra dove finisce il wafer e dove inizia il package. Foveros Direct consente picchi di bump inferiori a 10 micron con un aumento di un ordine di grandezza nella densità di interconnessione per il 3D stacking e la creazione di nuovi concetti per il partizionamento funzionale di stampi che prima non erano realizzabili. Foveros Direct è complementare a Foveros Omni ed è anchesso previsto per il 2023.

Gli annunci odierni confermano le intenzioni di Intel legate allo sviluppo delle tecnologie produttive del futuro e la volontà di mantenere la posizione di vertice tra i produttori di semiconduttori, non solo per le soluzioni a marchio Intel ma anche per espandere l'attività andando a proporre le proprie soluzioni anche a clienti: tra questi spicca AWS, annunciato quest'oggi quale il primo che utilizzerà le soluzioni di packaging Intel Foundry Services mentre Qualcomm utilizzerà il processo Intel A20 per la produzione dei propri chip.

Significativo quanto dichiarato da Pat Gelsinger durante la webcast dell'evento Intel Accelerated: "Finché non sarà esaurita la tavola periodica degli elementi, non smetteremo di perseguire la Legge di Moore nel nostro percorso di innovazione con la magia del silicio.

GIGABYTE GAMING A16, Raptor Lake e RTX 5060 Laptop insieme per giocare al giusto prezzo

GIGABYTE GAMING A16, Raptor Lake e RTX 5060 Laptop insieme per giocare al giusto prezzo iPhone 17 Pro: più di uno smartphone. È uno studio di produzione in formato tascabile

iPhone 17 Pro: più di uno smartphone. È uno studio di produzione in formato tascabile Intel Panther Lake: i processori per i notebook del 2026

Intel Panther Lake: i processori per i notebook del 2026 Settembre da primato per le auto elettriche: superata quota 2 milioni di unità vendute

Settembre da primato per le auto elettriche: superata quota 2 milioni di unità vendute Driver Windows più affidabili: Microsoft dà il via alle nuove regole sul WHCP

Driver Windows più affidabili: Microsoft dà il via alle nuove regole sul WHCP Scossa in casa Ubisoft: il leader di Assassin's Creed si dimette. Fine di un'epoca

Scossa in casa Ubisoft: il leader di Assassin's Creed si dimette. Fine di un'epoca Samsung HBM4E: fino a 3,25 TB/s di banda per le future GPU per l'intelligenza artificiale

Samsung HBM4E: fino a 3,25 TB/s di banda per le future GPU per l'intelligenza artificiale 76 con coupon: torna la scopa elettrica da 450W con accessori più venduta del Prime Day, oggi allo stesso prezzo

76 con coupon: torna la scopa elettrica da 450W con accessori più venduta del Prime Day, oggi allo stesso prezzo Intel Panther Lake, il marchio Core Ultra evolve: in arrivo i Core Ultra X

Intel Panther Lake, il marchio Core Ultra evolve: in arrivo i Core Ultra X Toshiba rompe la barriera dei 10 piatti e prepara hard disk da 40 TB

Toshiba rompe la barriera dei 10 piatti e prepara hard disk da 40 TB Risparmiate 140: Apple Mac mini con chip M4 a 589 su Amazon, il Mac più economico di tutti

Risparmiate 140: Apple Mac mini con chip M4 a 589 su Amazon, il Mac più economico di tutti Ultime ore per EUREKA J15 Ultra ed Evo Ultra svenduti su Amazon: top di gamma fino a 22.000Pa e lavaggio ad acqua calda, sotto i 500

Ultime ore per EUREKA J15 Ultra ed Evo Ultra svenduti su Amazon: top di gamma fino a 22.000Pa e lavaggio ad acqua calda, sotto i 500 6 tablet da 11" scontatissimi: da 99 a 151, non cercate altro sono questi i migliori su Amazon

6 tablet da 11" scontatissimi: da 99 a 151, non cercate altro sono questi i migliori su Amazon Crescent Island: la nuova GPU Intel Xe3P per l'inferenza AI ha 160 GB di LPDDR5X

Crescent Island: la nuova GPU Intel Xe3P per l'inferenza AI ha 160 GB di LPDDR5X Anche HONOR avrà il suo top di gamma compatto: tanta potenza e super batteria

Anche HONOR avrà il suo top di gamma compatto: tanta potenza e super batteria Google Gemini 3.0 potrebbe essere vicino: in rete spunta la possibile data di presentazione

Google Gemini 3.0 potrebbe essere vicino: in rete spunta la possibile data di presentazione

36 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoquesto qui cchèvordì:

"Significativo quanto dichiarato da Pat Gelsinger durante la webcast dell'evento Intel Accelerated: "Finché non sarà esaurita la tavola periodica degli elementi, non smetteremo di perseguire la Legge di Moore nel nostro percorso di innovazione con la magia del silicio”.

cioè che anche se gli elementi venissero scoperti fino al n. 215 loro perservereranno col silicio?

mi sembra un pochino troppo arrogante come piano di sviluppo...

o prevedono di fare processori con altri elementi? tipo Rame, Fosforo, Molibdeno, Piombo o Pradolinio?

se è ancora vivo il tale Moore della famosa legge, credo che si taglierà le mani tra una tagliola nanometrica periodica... (perchè lui era andato avanti solo col silicio e dovrà rifare tutti i calcoli...

L'unica cosa vera è che i (sono più di uno) PP a 10nm di Intel non sono a 10nm come si intendeva anni fa e che lo stesso vale per i 7nm di TSMC.

Tutto il resto è il solito oste che ti dice quanto sia buono il suo vino.

Ad esempio, Intel aveva dichiarato che il suo PP a 10nm permette di avere una densità di gate superiore al 7nm di TSMC ... ma poi nella pratica tale densità viene usata (quando viene usata) solo in alcuni tipi di circuiti e la maggior parte (se non tutto il chip) ha una densità minore.

Esempio lampante di leggere (forse) e non capire

Il loro i9 top di gamma desktop è sempre a 14nm e ce ne vuole per dire che abbia un rapporto performance per watt decente.

Tutto il resto è il solito oste che ti dice quanto sia buono il suo vino.

Ad esempio, Intel aveva dichiarato che il suo PP a 10nm permette di avere una densità di gate superiore al 7nm di TSMC ... ma poi nella pratica tale densità viene usata (quando viene usata) solo in alcuni tipi di circuiti e la maggior parte (se non tutto il chip) ha una densità minore.

La questione della densità reale rispetto a quella massima teorica vale per tutti i PP, non solo per quelli di Intel.

Interessante la questione dei nuovi sistemai di packaging che permettono di comporre in maniera completamente innovativa i vari die.

Chissà che non vedremo nuove forme di MCM senza costosi bus a livello energetico/latenze e quindi con performance molto vicine a quelle di die monolitici eliminando per sempre il problema di dover fare pizze funzionanti in un solo colpo per avere performance decenti.

Sarebbe una cosa che va ben oltre la ormai obsoleta legge di Moore.

-cit B&C

Chissà che non vedremo nuove forme di MCM senza costosi bus a livello energetico/latenze e quindi con performance molto vicine a quelle di die monolitici eliminando per sempre il problema di dover fare pizze funzionanti in un solo colpo per avere performance decenti.

Sarebbe una cosa che va ben oltre la ormai obsoleta legge di Moore.

Da questo punto di vista AMD ha fatto scuola. MCM è una idea vincente da più punti di vista: costi e flessibilità per primi. In futuro tutti useranno questo modello in varie forme.

-cit B&C

Se non conoscete la differenza di nomenclatura tra Intel e TSMC e neanche che sono anni che c'è una polemica riguardo all'uso dei numeri come nanometri per descrivere i PP (a cui a quanto pare Intel si è piegata allineandosi alla concorrenza), mi chiedo perché veniate qui a commentare.

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".