IDF Fall 2007, processori Octo Core e GPU Intel

Intel anticipa le caratteristiche di Nehalem, architettura del dopo Penryn, promettendo processori ad otto core, memory controller integrato ed un nuovo bus di comunicazione. Si fa strada l'idea di destinazioni d'uso del modulo Larrabee anche per schede video di fascia alta, in concorrenza con AMD e NVIDIA. Questo e altro ancora nel report del Day 1

di Alessandro Bordin , Andrea Bai pubblicato il 19 Settembre 2007 nel canale SistemiNVIDIAIntelAMD

Tick-tock

Oltre all'annuncio di novità tecnologiche e prodotti, l'Intel Developer Forum rappresenta spesso l'occasione per poter scoprire qualche informazione in più di ciò che accade "dietro le quinte" e di quali sono e come funzionano i meccanismi che permettono ad un colosso quale è Intel di percorrere e tracciare la strada della tecnologia.

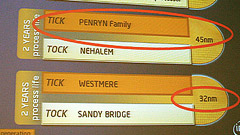

Ad aprire la sessione tecnica vi è la dimostrazione, non senza un pizzico di orgoglio, della validità del sistema "tick-tock", ovvero la strategia adottata da Intel per il rinnovamento generazionale dei propri processori. Il colosso di Santa Clara adotta infatti un "codice di condotta" estremamente rigoroso: l'adozione di un nuovo processo produttivo (la fase di "tick") avviene con una architettura ormai già collaudata mentre il passaggio ad una nuova architettura (la fase di "tock") avviene, viceversa, quando la produzione con un determinato processo è ormai avviata con ottimi risultati e rese elevate.

Ogni ciclo ha la durata di due anni: negli anni dispari viene affrontata la transizione verso un nuovo processo produttivo, mentre negli anni pari si da vita alla nuova architettura. Così è stato in passato, così avviene oggi con l'introduzione di Penryn a 45 nanometri ma basato su architettura Core che vedrà succedere Nehalem a 45 nanometri ma con architettura completamente nuova e così avverrà in futuro quando, con Westmere il debutto dei 32 nanometri sarà abbinato alla stessa architettura di Nehalem. Infine, con architettura nuova ma processo a 32 nanometri, vi sarà Sandy Bridge.

La produzione a 45 nanometri deve però molto alla scelta di utilizzare l'Afnio per la realizzazione dei gate dei transistor, un metallo caratterizzato da una elevata costante dielettrica K, che consente così di ridurre considerevolmente i problemi di leakage di corrente che si verificherebbero se si realizzassero, a queste dimensioni, gate tradizionali in diossido di silicio. Ovviamente la riduzione delle dimensioni dei gate dei transistor danno modo di ottenere una maggiore densità per chip e conseguentemente di aumentare le performance per watt.

Forza Horizon 6 Recensione: si vola in Giappone!

Forza Horizon 6 Recensione: si vola in Giappone! HONOR CHOICE AI Note, il registratore IA che si ricarica dallo smartphone

HONOR CHOICE AI Note, il registratore IA che si ricarica dallo smartphone Insta360 GO 3S Pack Retrò: l'azione incontra lo stile delle macchine a pellicola

Insta360 GO 3S Pack Retrò: l'azione incontra lo stile delle macchine a pellicola Il nuovo iPad è vicino: ecco quando arriva e quali saranno le novità

Il nuovo iPad è vicino: ecco quando arriva e quali saranno le novità Samsung prepara i nuovi Tab S12: il SoC è già confermato

Samsung prepara i nuovi Tab S12: il SoC è già confermato Xiaomi 17T e 17T Pro a un passo dal debutto: un leak conferma la data di lancio

Xiaomi 17T e 17T Pro a un passo dal debutto: un leak conferma la data di lancio Lo smartphone di Trump Mobile è pronto: le spedizioni sono partite questa settimana

Lo smartphone di Trump Mobile è pronto: le spedizioni sono partite questa settimana Top 10 Amazon weekend: 5 Mac in sconto e c'è anche il Neo, al 2 e 4 super offerte, robot scontatissimi, Pixel 10 Pro a -36% reale

Top 10 Amazon weekend: 5 Mac in sconto e c'è anche il Neo, al 2 e 4 super offerte, robot scontatissimi, Pixel 10 Pro a -36% reale_1_160.jpg) MacBook Neo è famoso per essere uno dei pochi prodotti Apple economici, e ora va per la prima volta in offerta

MacBook Neo è famoso per essere uno dei pochi prodotti Apple economici, e ora va per la prima volta in offerta AirPods Pro 3 a 199 su Amazon: un prezzo che sorprende per gli auricolari Apple più desiderati

AirPods Pro 3 a 199 su Amazon: un prezzo che sorprende per gli auricolari Apple più desiderati Un fondo di venture capital dice che l'apocalisse del lavoro AI è una fantasia. Non ne sarei così sicuro

Un fondo di venture capital dice che l'apocalisse del lavoro AI è una fantasia. Non ne sarei così sicuro Dashcam 4K, compressori, bloccadisco: le offerte Amazon di oggi per la propria auto o moto che conviene non lasciarsi sfuggire

Dashcam 4K, compressori, bloccadisco: le offerte Amazon di oggi per la propria auto o moto che conviene non lasciarsi sfuggire ECOVACS DEEBOT T80 OMNI a 499 e tutti gli altri robot aspirapolvere in offerta Amazon: specifiche e consigli per scegliere bene

ECOVACS DEEBOT T80 OMNI a 499 e tutti gli altri robot aspirapolvere in offerta Amazon: specifiche e consigli per scegliere bene Nuovi e scontati: MacBook Air M5 a -50 e -100, -150 sui MacBook Pro 14,2" con chip M5 16GB/1TB, con M5 Max -300

Nuovi e scontati: MacBook Air M5 a -50 e -100, -150 sui MacBook Pro 14,2" con chip M5 16GB/1TB, con M5 Max -300 Ottimo prezzo oggi per le Bose QuietComfort: minimo storico a 139 per gli iconici auricolari ANC

Ottimo prezzo oggi per le Bose QuietComfort: minimo storico a 139 per gli iconici auricolari ANC La fibra è sempre più diffusa e Iliad cresce ancora nel mobile: cosa dice il nuovo Osservatorio AGCOM

La fibra è sempre più diffusa e Iliad cresce ancora nel mobile: cosa dice il nuovo Osservatorio AGCOM