ARM a tutta sui 64 bit con i core Cortex-X4, Cortex-A720 e Cortex-A520

ARM punta a un futuro totalmente a 64 bit con i nuovi core Cortex-X4, Cortex-A720 e Cortex-A520 che vedremo nei futuri SoC per smartphone e non solo.

di Manolo De Agostini pubblicata il 30 Maggio 2023, alle 11:21 nel canale TelefoniaARM

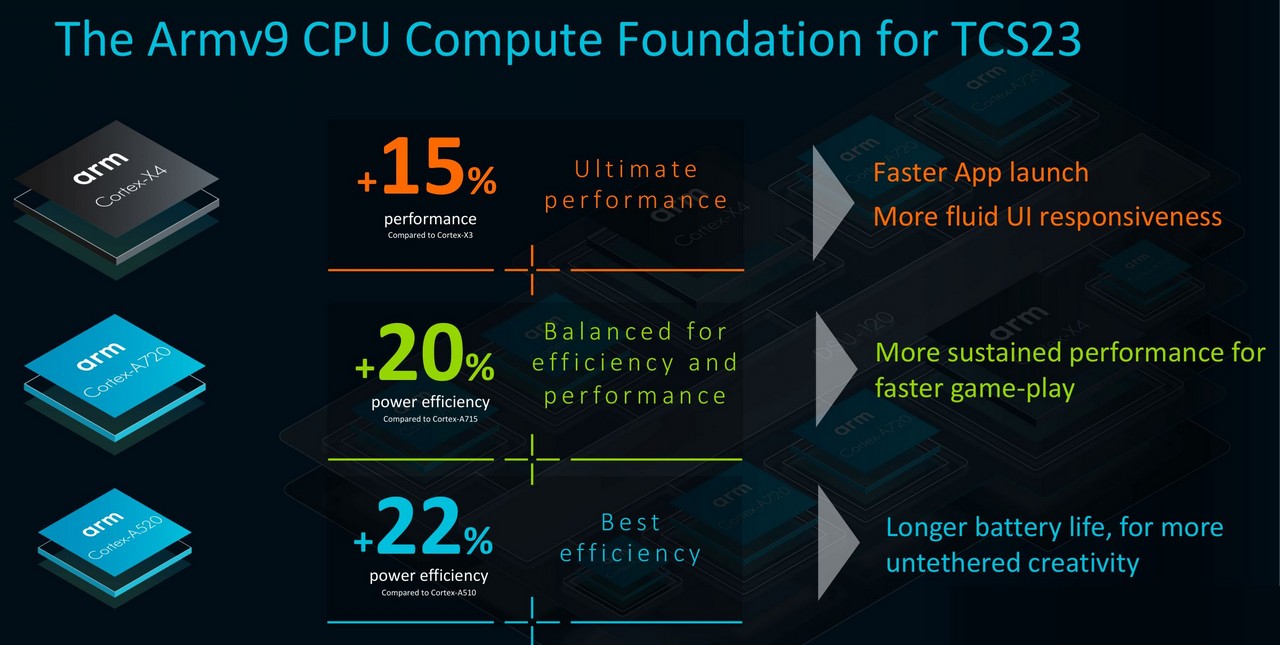

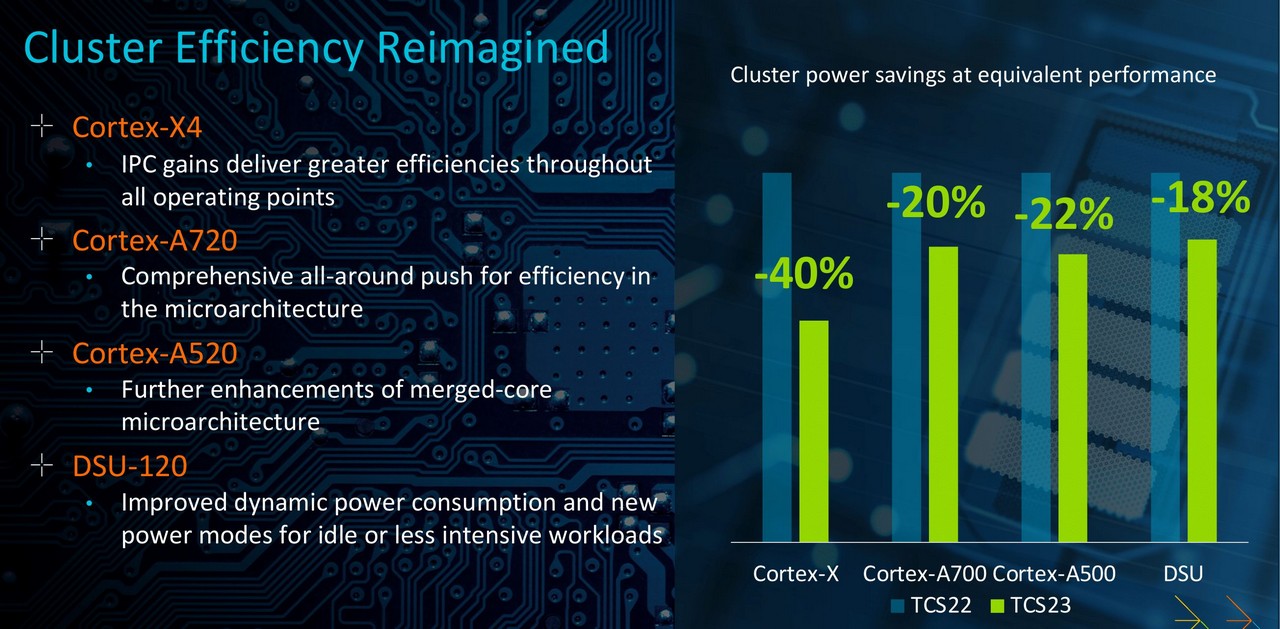

Cortex-X4, Cortex-A720 e Cortex-A520 - ma anche DSU-120 - sono le principali novità svelate dalla britannica ARM nelle scorse ore. Si tratta delle architetture che plasmeranno i SoC per smartphone, ma non solo, che vedremo prossimamente. I progetti nascono per sfruttare in particolar modo il processo produttivo a 3 nanometri.

Il passaggio completo al set di istruzioni AArch64 a 64-bit e alcuni miglioramenti per migliorare prestazioni ed efficienza sono le principali direttrici seguite dal colosso del chip mobile. Con l'ISA Armv9.2 la casa britannica elimina il supporto alle applicazioni a 32 bit, di conseguenza la società ha dovuto creare tre architetture - un core ad alte prestazioni, uno di medio livello e uno a basso consumo - per permettere ai propri clienti di creare un SoC totalmente a 64 bit.

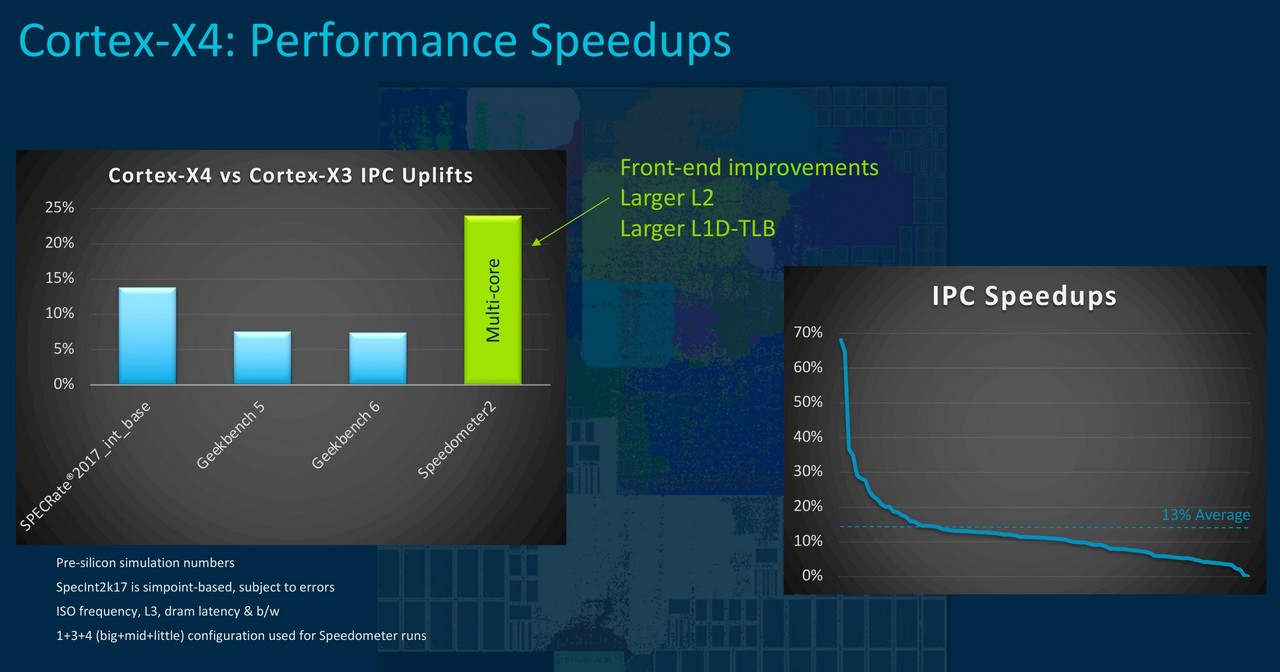

Il core Cortex-X4 è il progetto di punta, pensato per garantire le massime prestazioni e superare quanto garantito dal già ottimo Cortex-X3. Forte di una cache L2 maggiorata, 2 MB contro 1 MB, il nuovo core è in grado di migliorare le prestazioni e tenere a bada i consumi.

Da un punto di vista architetturale, ARM è intervenuta sul front end, con una dispatch width 10-wide anziché 6/8-wide del Cortex-X3, e ha ridotto la lunghezza della pipeline da 11 a 10 cicli. La casa britannica ha anche riprogettato il sistema di fetching delle istruzioni per ottenere maggiore efficienza. Inoltre, è stata migliorata anche l'unità di brach prediction.

Nel back-end è stato incrementato il numero di ALU da 6 a 8: sei sono ALU semplici per processare micro-ops a singolo ciclo, le altre due sono ALU complesse per processare istruzioni a due e più cicli. Questi sono però solo alcuni degli interventi, ve ne sono una miriade.

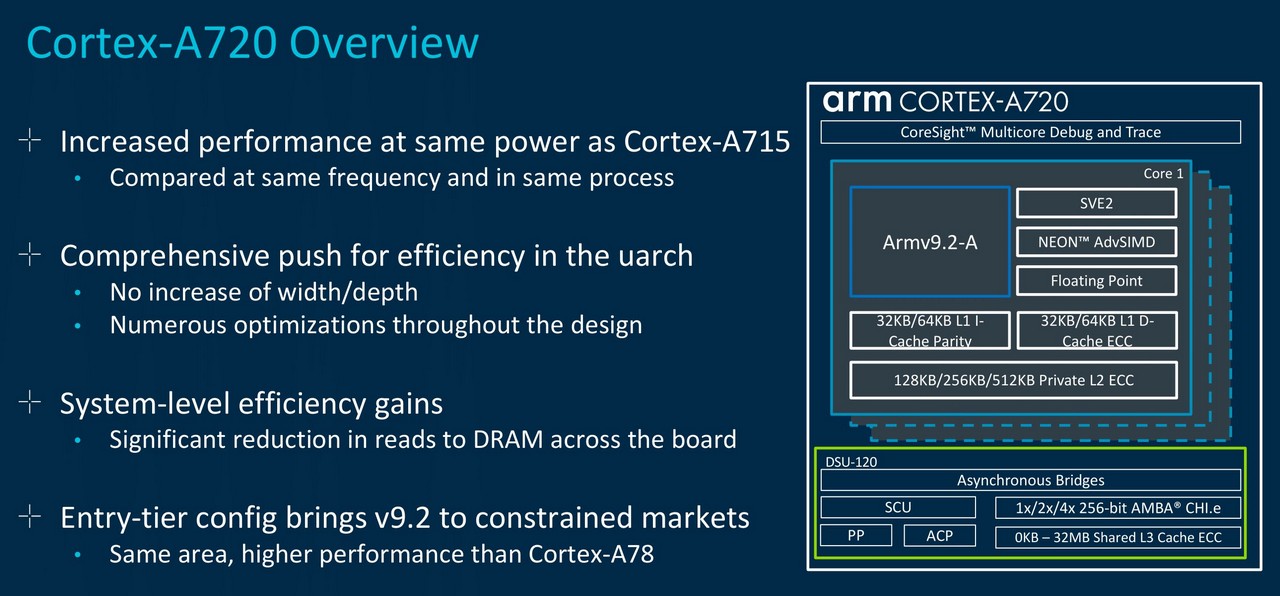

Cortex-A720 è probabilmente il meno innovativo del trio, in quanto già il Cortex-A715 era a 64 bit. Le migliorie apportate consentono anche in questo caso di migliorare le prestazioni di un 15% alla medesima frequenza rispetto al predecessore, a seconda del carico di lavoro. Rispetto al core dello scorso anno l'efficienza è stata migliorata del 20% grazie a una revisione del frontend.

Sulla stessa linea anche il Cortex-A520, quello pensato per garantire un'elevata efficienza. ARM assicura proprio grandi passi avanti nell'efficienza, con un +22% rispetto al Cortex-A510 fermo restando lo stesso processo produttivo e frequenza operativa. A parità di consumo, invece, A520 dovrebbe essere l'8% più performante.

La DynamIQ Shared Unit-120 (DSU-120) è il nuovo "core complex" che permetterà di creare SoC basati sui vari core di cui vi abbiamo parlato al fine di aggredire ambiti maggiormente multi-thread. Rispetto al passato supporta fino a 14 core, anziché 12, e fino a 32 MB di cache L3 condivisa, il doppio rispetto alla DSU-110.

A seconda quindi che il SoC nasca per l'ambito notebook o smartphone, i partner di ARM avranno molteplici possibilità di configurazione: nei chip più complessi si potranno integrare fino a 4 core Cortex-X4, altrettanti Cortex-A720 e ben 6 Cortex-A520.

Da segnalare, infine, che ARM ha annunciato anche la GPU Immortalis-G720, anch'essa in grado di migliorare le prestazioni del 15% e l'efficienza livello di sistema del 40% grazie a un uso minore della bandwidth di memoria.

Recensione vivo X300 Pro: è ancora lui il re della fotografia mobile, peccato per la batteria

Recensione vivo X300 Pro: è ancora lui il re della fotografia mobile, peccato per la batteria Lenovo Legion Go 2: Ryzen Z2 Extreme e OLED 8,8'' per spingere gli handheld gaming PC al massimo

Lenovo Legion Go 2: Ryzen Z2 Extreme e OLED 8,8'' per spingere gli handheld gaming PC al massimo AWS re:Invent 2025: inizia l'era dell'AI-as-a-Service con al centro gli agenti

AWS re:Invent 2025: inizia l'era dell'AI-as-a-Service con al centro gli agenti Il nucleo della cometa interstellare 3I/ATLAS potrebbe avere un diametro compreso tra gli 820 metri e i 1050 metri

Il nucleo della cometa interstellare 3I/ATLAS potrebbe avere un diametro compreso tra gli 820 metri e i 1050 metri La Russia potrebbe sviluppare un'arma per distruggere più satelliti, compresi quelli Starlink

La Russia potrebbe sviluppare un'arma per distruggere più satelliti, compresi quelli Starlink Manda la RAM Corsair in assistenza, riceve indietro due moduli di memoria finti

Manda la RAM Corsair in assistenza, riceve indietro due moduli di memoria finti ASUS ROG G1000 con 'AniMe Holo': saranno gli ologrammi a dominare la presentazione al CES 2026?

ASUS ROG G1000 con 'AniMe Holo': saranno gli ologrammi a dominare la presentazione al CES 2026? Un test di longevità ha messo alla prova 102 modelli di TV per 3 anni: promossi gli OLED

Un test di longevità ha messo alla prova 102 modelli di TV per 3 anni: promossi gli OLED Incat inizia i test dell'incredibile traghetto elettrico più grande del mondo

Incat inizia i test dell'incredibile traghetto elettrico più grande del mondo LG Sound Suite: al CES il sistema audio modulare con Dolby Atmos FlexConnect

LG Sound Suite: al CES il sistema audio modulare con Dolby Atmos FlexConnect Avengers Doomsday, il primo trailer è ufficialmente online: il ritorno di un personaggio tanto amato

Avengers Doomsday, il primo trailer è ufficialmente online: il ritorno di un personaggio tanto amato La crisi delle memorie non farà sconti al mercato PC: atteso un calo netto delle vendite nel 2026

La crisi delle memorie non farà sconti al mercato PC: atteso un calo netto delle vendite nel 2026 Il trailer più atteso dell'anno è qui. "Odissea" di Christopher Nolan ha la data ufficiale in Italia

Il trailer più atteso dell'anno è qui. "Odissea" di Christopher Nolan ha la data ufficiale in Italia I gamer vogliono i monitor OLED: soprattutto ASUS, poi Samsung

I gamer vogliono i monitor OLED: soprattutto ASUS, poi Samsung Samsung alza lasticella dei televisori tra colori, AI e nuovi tagli da 55 a 155 pollici: al CES 2026 la nuova linea Micro RGB

Samsung alza lasticella dei televisori tra colori, AI e nuovi tagli da 55 a 155 pollici: al CES 2026 la nuova linea Micro RGB Energie rinnovabili 2025: quasi 42% del totale, il fotovoltaico sorpassa l'idroelettrico

Energie rinnovabili 2025: quasi 42% del totale, il fotovoltaico sorpassa l'idroelettrico Le auto elettriche volano in tutta Europa, ed è europeo il primo produttore a novembre

Le auto elettriche volano in tutta Europa, ed è europeo il primo produttore a novembre

1 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoDevi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".