Cosa aspettarsi dal processo produttivo N2 (2 nanometri) di TSMC

TSMC ha parlato nelle scorse settimane del processo N2, meglio noto come 2 nanometri. Atteso nella seconda parte del 2025, porterà i nuovi transistor GAAFET e miglioramenti sul fronte delle prestazioni e dei consumi. Delude l'incremento della densità e slitta l'alimentazione dal retro.

di Manolo De Agostini pubblicata il 01 Luglio 2022, alle 09:41 nel canale ProcessoriTSMC

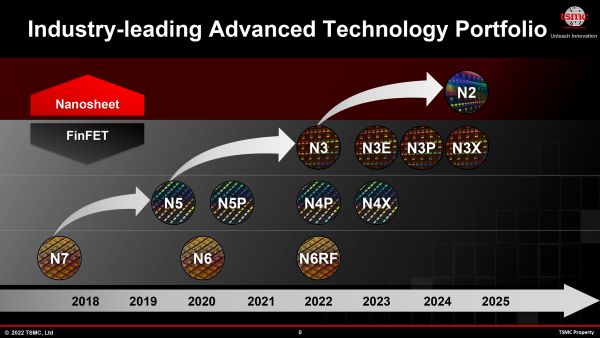

Il produttore di chip per conto terzi TSMC ha recentemente svelato i dettagli su N2, il processo produttivo che "volgarmente" viene identificato nei 2 nanometri. La nuova tecnologia produttiva dovrebbe debuttare in "risk production" nella seconda parte del 2024, mentre la produzione in volumi prenderà il via un anno più tardi.

La notizia importante è che N2 rappresenterà il primo processo a implementare i nuovi transistor GAAFET di TSMC. A tal proposito è bene ricordare come Samsung abbia annunciato nelle scorse ore l'avvio della produzione iniziale a 3 nanometri con i nuovi transistor GAAFET, nell'implementazione proprietaria noti come MBCFET. L'azienda sudcoreana punta quindi a bruciare TSMC e Intel, quest'ultima attesa con i suoi "RibbonFET" nel 2024.

Per il nuovo processo N2 TSMC prevede importanti miglioramenti che ridurranno il consumo energetico dei chip prodotti, aumentando contestualmente la densità e la velocità dei transistor, seppur su una scala più contenuta. Uso intensivo della litografia all'ultravioletto estremo (EUV), i nuovi transistor e in un momento successivo non meglio precisato l'implementazione della "backside power delivery", ovvero un'alimentazione dal retro che ottimizza la trasmissione del segnale eliminando la necessità far passare l'alimentazione al lato anteriore del wafer, contribuiranno alle innovazioni che vedremo sul mercato tra alcuni anni.

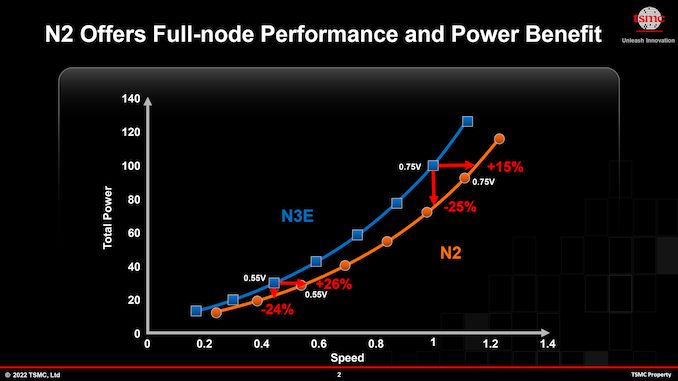

Venendo ai numeri, il processo N2 di TSMC permetterà ai designer di incrementare le prestazioni del 10-15% fermo restando lo stesso consumo rispetto al processo N3E basato su transistor FinFET. Allo stesso tempo sarà possibile ridurre i consumi del 25-30% mantenendo la stessa frequenza, il tutto incrementando la densità del 10% sempre rispetto al processo N3E. Ed è proprio quest'ultimo punto a far storcere il naso agli addetti ai lavori che si aspettavano i progressi maggiori.

TSMC, infine, promette la possibilità di integrare facilmente i chip prodotti con processo N2 all'interno di package costituiti da chiplet realizzati con processi produttivi differenti. Come illustrato più volte in passato e in base ai progetti in seno a NVIDIA, AMD e Intel, il rallentamento nell'aumento della densità e il costo sempre più alto delle tecnologie produttive porterà a un ricorso sempre più esteso alla realizzazione di design "componibili", fatti di tanti chip differenti sullo stesso package. L'era monolitica, ovvero di chip con disparate funzionalità integrate in un unico design, sembra agli sgoccioli, almeno nel settore delle alte prestazioni.

OPPO Find X9 Pro: il camera phone con teleobiettivo da 200MP e batteria da 7500 mAh

OPPO Find X9 Pro: il camera phone con teleobiettivo da 200MP e batteria da 7500 mAh DJI Romo, il robot aspirapolvere tutto trasparente

DJI Romo, il robot aspirapolvere tutto trasparente DJI Osmo Nano: la piccola fotocamera alla prova sul campo

DJI Osmo Nano: la piccola fotocamera alla prova sul campo Anche gli USA inseguono l'indipendenza: una startup americana promette un'alternativa migliore di ASML per la produzione di chip

Anche gli USA inseguono l'indipendenza: una startup americana promette un'alternativa migliore di ASML per la produzione di chip TikTok: i content creator guadagneranno di più con i nuovi strumenti basati sull'IA

TikTok: i content creator guadagneranno di più con i nuovi strumenti basati sull'IA Nothing Phone (3a) Lite disponibile, ma stavolta è solo un rebrand

Nothing Phone (3a) Lite disponibile, ma stavolta è solo un rebrand Emissioni globali per la prima volta in calo secondo l'ONU, ma l'obiettivo è ancora troppo distante

Emissioni globali per la prima volta in calo secondo l'ONU, ma l'obiettivo è ancora troppo distante Bancomat lancia Eur-Bank: la stablecoin bancaria italiana conforme a MiCAR

Bancomat lancia Eur-Bank: la stablecoin bancaria italiana conforme a MiCAR NVIDIA supera i 5.000 miliardi di dollari: è la prima azienda al mondo a farlo

NVIDIA supera i 5.000 miliardi di dollari: è la prima azienda al mondo a farlo I ransomware fanno meno paura: solo un'azienda su 4 cede al riscatto

I ransomware fanno meno paura: solo un'azienda su 4 cede al riscatto Intel Nova Lake-S: i dissipatori delle precedenti generazioni saranno compatibili, stavolta è 'ufficiale'

Intel Nova Lake-S: i dissipatori delle precedenti generazioni saranno compatibili, stavolta è 'ufficiale' 1X Technologies apre i preordini per NEO, il primo robot umanoide domestico. Un pericolo per la privacy

1X Technologies apre i preordini per NEO, il primo robot umanoide domestico. Un pericolo per la privacy Tesla Cybercab cambia rotta: nel taxi del futuro anche volante e pedali, senza guida autonoma completa

Tesla Cybercab cambia rotta: nel taxi del futuro anche volante e pedali, senza guida autonoma completa L'industria dell'auto europea a pochi giorni dalla catastrofe: stop delle linee di assemblaggio imminente

L'industria dell'auto europea a pochi giorni dalla catastrofe: stop delle linee di assemblaggio imminente VMware tra cloud privato e nuovi modelli di business: cosa si è detto a Explore on Tour 2025 Parigi

VMware tra cloud privato e nuovi modelli di business: cosa si è detto a Explore on Tour 2025 Parigi Amazon Haul lancia il colpo di genio: prendi 2 prodotti e paghi il secondo la metà codice segreto dentro

Amazon Haul lancia il colpo di genio: prendi 2 prodotti e paghi il secondo la metà codice segreto dentro

5 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoIl fatto è che i PP non migliorano più come un tempo. Il problema della densità si risolve con le tecnologie di packaging di più die, ma purtroppo per i consumi non c'è soluzione: più prestazioni con più die senza il relativo miglioramento del PP in tale senso vuol dire più consumi.

Ecco allora che appaiono rumor di schede grafiche da 600 e + W (follia!) o comunque di consumi intorno ai 450W per singola GPU come se fosse cosa normale.

E ne abbiamo un esempi anche con la piattaforma AM5 di AMD dove i TDP massimi sono stati elevati e non di poco.

Si va verso un mondo in cui l'aumento di prestazioni è parallelo a quello dei consumi.

E' finita la pacchia. Altro che "futuro eco-sostenibile", "diminuiamo i consumi", "Il futuro è green".

Magari questa rottura con il passato porterà anche a qualcosa di buono, tipo che sopravviverà chi ha l'efficienza maggiore e così, alla fine, l'architettura x86 avrà il suo bel da fare per mantenersi leader delle vendite anche nel mercato consumer.

P.S: comunque TSMC è in ritardo sulla implementazione dei GAAFet. Samsung è Intel l'hanno anticipata di molto, quindi o spera di avere una implementazione perfetta già al primo giro, oppure si ritroverà a rincorrere la concorrenza che, quando lei debutterà, avrà già 1 o 2 interazioni della tecnologia già in atto. I GAAFet possono essere il nuovo (e a guardare anche l'unico per ora) metodo per avanzare con i PP in maniera sensibile, e adottarli con ritardo potrebbe portare a problemi nel breve, sempre ovviamente che gli altri li implementino in maniera decente.

P.P.S: N2 nel tardo 2025 vuol dire che le nuove architetture di AMD/Nvidia basate sugli N3 li vedremo nel 2026. Altro che nuovi metodi di packaging per riuscire a creare una nuova serie... si prospetta una bella lotta a suon di modifiche profonde delle architetture per massimizzare le prestazioni vs consumi vs costi. E ho i miei seri dubbi che questi ultimi siano la priorità.

Il fatto è che i PP non migliorano più come un tempo. Il problema della densità si risolve con le tecnologie di packaging di più die, ma purtroppo per i consumi non c'è soluzione: più prestazioni con più die senza il relativo miglioramento del PP in tale senso vuol dire più consumi.

Ecco allora che appaiono rumor di schede grafiche da 600 e + W (follia!) o comunque di consumi intorno ai 450W per singola GPU come se fosse cosa normale.

E ne abbiamo un esempi anche con la piattaforma AM5 di AMD dove i TDP massimi sono stati elevati e non di poco.

Si va verso un mondo in cui l'aumento di prestazioni è parallelo a quello dei consumi.

E' finita la pacchia. Altro che "futuro eco-sostenibile", "diminuiamo i consumi", "Il futuro è green".

Magari questa rottura con il passato porterà anche a qualcosa di buono, tipo che sopravviverà chi ha l'efficienza maggiore e così, alla fine, l'architettura x86 avrà il suo bel da fare per mantenersi leader delle vendite anche nel mercato consumer.

Se fosse come dici te, non é che é finita la pacchia... é finita... kaputt... addio... speriamo esista davvero il paradiso.

È altrettanto vero che questo vale per i prodotti top di gamma. Esattamente come tutti non guidano Ferrari, così la stragrande maggioranza della gente usa prodotti a consumi e potenza contenuti.

E questo è ancor più vero al giorno d'oggi, dove un nuc con Pentium n6005 ha già tutte le potenzialità per soddisfare le esigenze informatiche dell'utente medio, per dire..

E questo è ancor più vero al giorno d'oggi, dove un nuc con Pentium n6005 ha già tutte le potenzialità per soddisfare le esigenze informatiche dell'utente medio, per dire..

Vero, ma il progresso tecnologico non è il NUC di 6 anni fa.

Il NUC è il derivato a basso costo di quello che è stato sviluppato come top gamma 3 o 4 anni prima. Se oggi non hai top gamma o leading technology che di si voglia, tra 3 o 4 anni rimarrai con quello che hai ora.

E se vorrai progredire, visto che la tecnologia dei PP è rallentata tantissimo, dovrai sborsare diversi quattrini per mettere più silicio e consumare più corrente.

https://seekingalpha.com/article/45...nother-headwind

«It's important to note that even though SMIC is not able to acquire EUV lithography systems, TSMC made its N7 without EUV, using DUV 193 nm ArF Immersion lithography.»

«Prior to sanctions, SMIC announced what it called its next node N+1, claiming that it offers a 20% increase in performance, power consumption reduction of 57%, a reduced logic area by 63%, and SoC (System on a Chip) area reduction by 55% over its 14nm node, according to an October 15, 2020 press release from China.org.cn.

Understandably SMIC has been tight lipped about its N+1 process in light of current sanctions and rumors of additional ones. With that in mind, one can estimate SMICs current node production by the cadence of node transitions of TSMC and other competitors.

In Table 2, I show that all three companies are on a 1-1.5 year cadence in introducing an improved process or a new node. Translating that data to SMIC, which was in high volume production at 14nm in November 2019, the company should have transitioned to its N+1 node in 1Q 2021 and then the N+2 node in 2Q 2022. I estimate the N+1 node is at 8nm and the N+2 node is at 7nm.»

Che impatto può avere la maggiore complessità per raggiungere il nodo N+2 usando solo la litografia DUV 193 nm ArF?

P.S.io ho disabilitato il js per vedere il sito.

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".