AMD Fusion: preview di un sistema Brazos - parte 1

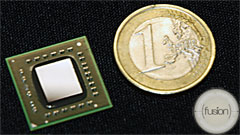

Nuove informazioni sulle prime soluzioni della famiglia AMD Fusion emergono a circa 2 mesi dalla presentazione ufficiale. In questa preview forniremo dettagli sull'architettura delle piattaforme Brazos, in attesa di poter pubblicare le prime rilevazioni prestazionali di una APU dual core con GPU integrata

di Paolo Corsini pubblicato il 09 Novembre 2010 nel canale ProcessoriAMD

Architettura Bobcat

Teoricamente l'architettura Bobcat è stata sviluppata da AMD anche pensando a modalità di utilizzo che contengano il consumo entro 1 Watt, attraverso un contenimento della tensione di alimentazione oltre che della frequenza di clock complessiva. E' quantomeno possibile che AMD possa decidere di presentare specifiche versioni di processore con architettura Bobcat capaci di consumi contenuti entro 1 Watt solo in un secondo tempo, in funzione di specifiche esigenze da parte dei propri partner commerciali. Il riferimento diretto è il mercato delle soluzioni Tablet PC, che così tanto interesse sta generando in questo periodo, proposte per le quali alcune specifiche versioni di APU Fusion potrebbero permettere di ottenere un ottimi bilanciamento prestazionale tra CPU e GPU. AMD sembra tenere una posizione di basso profilo su questo tema, identificando nelle soluzioni Bobcat una opportunità tecnologica per entrare in questo settore ma allo stesso tempo rimarcando come siano necessarie ulteriori innovazioni in quanto disponibile al momento con le soluzioni Ontario affinché i consumi possano ridurre ulteriormente, sia come TDP sia come idle, assicurando quell'autonomia che gli utenti di Tablet richiedono.

L'architettura Bobcat è del tipo out of order, comune quindi alla maggior parte dei moderni processori x86 presenti sul mercato con l'unica significativa eccezione rappresentata dalle soluzioni Intel Atom. Questo approccio permette di ottenere migliori prestazioni velocistiche, a scapito di un lieve incremento nei consumi complessivi, grazie alla possibilità del processore di riorganizzare le istruzioni da eseguire in modo tale che la loro esecuzione sia la più efficiente possibile in termini di prestazioni velocistiche. Pensiamo quindi alle soluzioni Bobcat come ad un ideale compromesso tra consumi e ridotte dimensioni delle soluzioni Intel Atom, abbinati alla potenza elaborativa di una cpu x86 di tipo out of order. Un approccio di questo tipo, del resto, è stato seguito anche dalla taiwanese VIA con le proprie soluzioni della famiglia Nano, proposte out of order che sono state posizionate quale dirette concorrenti delle CPU Intel Atom.

Bobcat utilizza un design dual issue, con due pipeline a 15 fasi che sono molto simili a quelle a 16 fasi implementate da Intel nell'architettura Atom. Ovviamente rimane la notevole differenza tra le due dato dal design out of order, scelta tecnica che permetterà di avere livelli prestazionali, a parità di frequenza di clock, ben più elevati in Bobcat rispetto ad Atom utilizzando applicazioni single threaded. Nel confronto con Atom segnaliamo la scelta di AMD di non introdurre alcun tipo di tecnologia simile a quella HyperThreading, integrata invece nelle soluzioni Atom, per non dover incrementare il numero complessivo di transistor e la superficie del die; per Intel, del resto, l'adozione di HyperThreading nelle CPU Atom è stata una scelta pressoché obbligata per assicurare un incremento delle prestazioni, limitate dall'architettura in-order.

Le cache integrate in Bobcat sono di 2 livelli: quella L1 è a due blocchi da 32 Kbytes ciascuno, rispettivamente per dati e istruzioni, del tipo associativa a 8 vie con latenza di 3 cicli di clock, mentre quella L2 è da 512 Kbytes di dimensione associativa a 16 vie, con latenza di 17 cicli di clock.

In termini di ISA Bobcat supporta i set di istruzioni SSE sino alla release 3; ulteriori evoluzioni saranno possibili con i futuri progressi dell'architettura nei prossimi anni, ma per il momento AMD ha ritenuto sufficiente limitare il supporto alle istruzioni SSE3 in considerazione del target di riferimento di questa classe di processori. Segnaliamo l'assenza del set di istruzioni 3DNow!, adottato per la prima volta da AMD con le cpu della famiglia K6. Dal punto di vista prestazionale questa mancanza non ha ripercussioni dirette, in quanto questo set di istruzioni è stato superato nel corso del tempo da quelle SSE; secondo AMD potrebbero tuttavia venirsi a creare limitazioni con alcuni software non recenti, soprattutto in ambito multimedia, che non vedendo supporto al set di istruzioni 3DNow! potrebbero non riconoscere correttamente le cpu con architettura Bobcat e quindi potenzialmente ottenere prestazioni non allineate a quanto teoricamente possibile.

Per minimizzare il livello di consumo complessivo di questi core AMD ha implementato varie tecnologie; segnaliamo quelle di clock gating e power gating, oltre a stati di tipo low power ai quali il sistema può accedere per contenere al massimo il livello di consumo in idle. A completare le funzionalità una serie di innovazioni micro-architetturali che riducono al minimo i trasferimenti di dati interni al chip, oltre a ridurre il numero di loro letture allo stretto indispensabile: l'approccio è quindi quello di fare in modo che quante più aree possibili del chip vengano mantenute in idle durante l'elaborazione, così da contenere al massimo i consumi.

OPPO Find X9 Pro: il camera phone con teleobiettivo da 200MP e batteria da 7500 mAh

OPPO Find X9 Pro: il camera phone con teleobiettivo da 200MP e batteria da 7500 mAh DJI Romo, il robot aspirapolvere tutto trasparente

DJI Romo, il robot aspirapolvere tutto trasparente DJI Osmo Nano: la piccola fotocamera alla prova sul campo

DJI Osmo Nano: la piccola fotocamera alla prova sul campo Xbox in caduta libera: vendite in calo del 29%, ma Microsoft sorride lo stesso

Xbox in caduta libera: vendite in calo del 29%, ma Microsoft sorride lo stesso Le immagini nell'occhio dell'uragano Melissa catturate da una Canon EOS R5 e da un iPhone 16 Pro Max

Le immagini nell'occhio dell'uragano Melissa catturate da una Canon EOS R5 e da un iPhone 16 Pro Max Anche gli USA inseguono l'indipendenza: una startup americana promette un'alternativa migliore di ASML per la produzione di chip

Anche gli USA inseguono l'indipendenza: una startup americana promette un'alternativa migliore di ASML per la produzione di chip TikTok: i content creator guadagneranno di più con i nuovi strumenti basati sull'IA

TikTok: i content creator guadagneranno di più con i nuovi strumenti basati sull'IA Nothing Phone (3a) Lite disponibile, ma stavolta è solo un rebrand

Nothing Phone (3a) Lite disponibile, ma stavolta è solo un rebrand Emissioni globali per la prima volta in calo secondo l'ONU, ma l'obiettivo è ancora troppo distante

Emissioni globali per la prima volta in calo secondo l'ONU, ma l'obiettivo è ancora troppo distante Bancomat lancia Eur-Bank: la stablecoin bancaria italiana conforme a MiCAR

Bancomat lancia Eur-Bank: la stablecoin bancaria italiana conforme a MiCAR NVIDIA supera i 5.000 miliardi di dollari: è la prima azienda al mondo a farlo

NVIDIA supera i 5.000 miliardi di dollari: è la prima azienda al mondo a farlo I ransomware fanno meno paura: solo un'azienda su 4 cede al riscatto

I ransomware fanno meno paura: solo un'azienda su 4 cede al riscatto Intel Nova Lake-S: i dissipatori delle precedenti generazioni saranno compatibili, stavolta è 'ufficiale'

Intel Nova Lake-S: i dissipatori delle precedenti generazioni saranno compatibili, stavolta è 'ufficiale' 1X Technologies apre i preordini per NEO, il primo robot umanoide domestico. Un pericolo per la privacy

1X Technologies apre i preordini per NEO, il primo robot umanoide domestico. Un pericolo per la privacy Tesla Cybercab cambia rotta: nel taxi del futuro anche volante e pedali, senza guida autonoma completa

Tesla Cybercab cambia rotta: nel taxi del futuro anche volante e pedali, senza guida autonoma completa L'industria dell'auto europea a pochi giorni dalla catastrofe: stop delle linee di assemblaggio imminente

L'industria dell'auto europea a pochi giorni dalla catastrofe: stop delle linee di assemblaggio imminente