30 miliardi di transistor in un chip: IBM dimostra per la prima volta i 5 nanometri con nanofogli di silicio

Assieme a Samsung e Globalfoundries IBM offre la prima dimostrazione della possibilità di realizzare chip a 5 nanometri con architettura basata su nanofogli di silicio e proprietà elettriche superiori all'attuale architettura FinFET

di Andrea Bai pubblicata il 05 Giugno 2017, alle 17:41 nel canale ProcessoriIBMSamsungGlobalfoundries

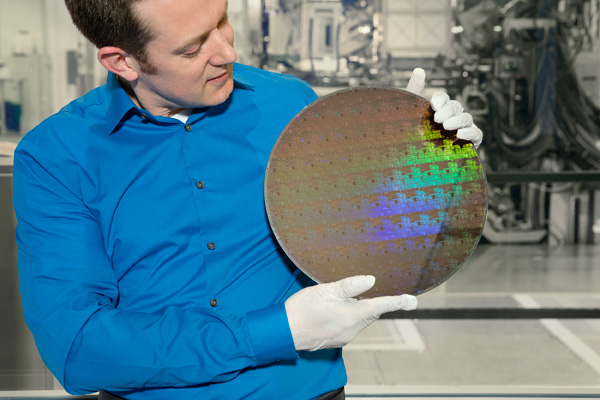

IBM, assieme a Globalfoundries e Samsung nel contesto della Research Alliance, hanno annunciato di aver sviluppato un nuovo processo e una nuova architettura che porterà alla realizzazione di transistor con nanofogli di silicio, un elemento cruciale per procedere verso la realizzazione di chip a 5 nanometri, superando i limiti fisiologici posti dalle attuali tecnologie e architetture. L'annuncio arriva a meno di due anni dallo sviluppo di un chip di test a 7 nanometri con 20 miliardi di transistor e prepara il terreno per la realizzazione di 30 miliardi di switch su un chip dalle dimensioni di un'unghia.

Arvind Krishna, senior vice president Hybrid Cloud e responsabile IBM Research, ha commentato: "Nei prossimi anni per rispondere alle necessità del cognitive e cloud computing sarà fondamentale un passo avanti nella tecnologia dei semiconduttori. Questo è il motivo per il quale IBM ha volto l'attenzione verso nuove e differenti architetture e materiali capaci di spingere avanti i limiti del settore, e portandoli sul mercato applicati a tecnologie come mainframe e sistemi cognitivi".

I ricercatori della Research Alliance coordinata da IBM hanno utilizzato una pila di nanofogli di silicio come struttura del transistor al posto della tradizionale architettura FinFET, usata per la realizzazione dei semiconduttori fino al nodo di processo a 7 nanometri. Il cambio di prospettiva è stato necessario poiché le tecnologie attuali non permettono, per limiti fisici, di poter scalare oltre nella rincorsa alla miniaturizzazione.

La Research Alliance ha usato, così come il precedente chip di test a 7 nanometri e 20 miliardi di transistor, la tecnologia Extreme Ultraviolet anche per la nuova architettura a nanofogli. L'impiego della litografia EUV permette di regolare in continuo lo spessore dei nanofogli, con un singolo processo produttivo o all'interno di un solo progetto. Questa particolarità offre la possibilità di regolare con precisione le prestazioni e la potenza per circuiti specifici, a differenza di quanto avviene oggi con la produzione di transistor basati sull'architettura FinFET, poiché la corrente è limtata dall'altezza delle alette. E' per questo motivo che i chip FinFET possono spingersi al massimo fino ai 5 nanometri, poiché la riduzione dello spazio tra le alette non porta ad un incremento del flusso di corrente o prestazioni maggiori.

Se messa a confronto con il processo a 10nm attualmente disponibile sul mercato, la tecnologia a 5nm basata su nanofogli di silicio è capace di offrire un incremento prestazionale del 40% a parità di consumi, o un risparmio energetico del 75% a parità di prestazioni: tutte caratteristiche che permetteranno sempre di più di rispondere alla domanda per i sistemi di Intelligenza Artificiale, per la realtà virtuale e per i dispositivi mobile. E' da oltre 10 anni che IBM Research ha sperimentato la tecnologia a nanofogli di silicio: i risultati di questo lavoro rappresentano la prima dimostrazione nel settore dei semiconduttori della fattibilità di progettazione e produzione di circuiteria logica basata su nanofogli con proprietà elettriche superiori all'architettura FinFET.

Quando sarà possibile vedere le prime concretizzazioni di questa dimostrazione? E' difficile dare delle indicazioni, ma è bene osservare che ancora non sono disponibili sul mercato chip a 7 nanometri (i primi esemplari sono attesi a 2018 inoltrato) e quindi è ragionevole immaginare che per i 5 nanometri sarà necessario attendere fino almeno al 2020.

La rivoluzione dei dati in tempo reale è in arrivo. Un assaggio a Confluent Current 2025

La rivoluzione dei dati in tempo reale è in arrivo. Un assaggio a Confluent Current 2025 SAP Sapphire 2025: con Joule l'intelligenza artificiale guida app, dati e decisioni

SAP Sapphire 2025: con Joule l'intelligenza artificiale guida app, dati e decisioni Dalle radio a transistor ai Micro LED: il viaggio di Hisense da Qingdao al mondo intero

Dalle radio a transistor ai Micro LED: il viaggio di Hisense da Qingdao al mondo intero Router e ripetitori AVM FRITZ! da 30 su Amazon: ecco tutte le offerte da non perdere

Router e ripetitori AVM FRITZ! da 30 su Amazon: ecco tutte le offerte da non perdere Adulting 101: i corsi per imparare come era la vita fino a qualche anno fa

Adulting 101: i corsi per imparare come era la vita fino a qualche anno fa Blue Origin ha lanciato con successo la missione suborbitale NS-32 con New Shepard

Blue Origin ha lanciato con successo la missione suborbitale NS-32 con New Shepard L'amministrazione Trump ha ritirato la candidatura di Jared Isaacman come amministratore della NASA

L'amministrazione Trump ha ritirato la candidatura di Jared Isaacman come amministratore della NASA La NASA potrebbe chiudere le missioni OSIRIS-APEX, New Horizons e Juno cancellandone altre per risparmiare soldi

La NASA potrebbe chiudere le missioni OSIRIS-APEX, New Horizons e Juno cancellandone altre per risparmiare soldi Trump vieta anche la vendita di software per la progettazione di chip alle società cinesi

Trump vieta anche la vendita di software per la progettazione di chip alle società cinesi Le migliori offerte del weekend Amazon: portatili, robot, iPhone, Kindle ai prezzi più bassi di sempre

Le migliori offerte del weekend Amazon: portatili, robot, iPhone, Kindle ai prezzi più bassi di sempre Dreame L40 Ultra a 699, prezzo shock: vale quasi quanto lX40 Ultra da 999 (ma costa 300 in meno!)

Dreame L40 Ultra a 699, prezzo shock: vale quasi quanto lX40 Ultra da 999 (ma costa 300 in meno!) AMD Radeon RX 9060 XT: fino al 31% più veloce della RX 7600 XT nei primi benchmark

AMD Radeon RX 9060 XT: fino al 31% più veloce della RX 7600 XT nei primi benchmark Blink Outdoor 4 e Ring Intercom in super offerta su Amazon: come rendere sicura la casa spendendo poco

Blink Outdoor 4 e Ring Intercom in super offerta su Amazon: come rendere sicura la casa spendendo poco Oggi in sconto Fire TV Stick HD ed Echo Show 5, la combo perfetta per iniziare a rendere smart la casa

Oggi in sconto Fire TV Stick HD ed Echo Show 5, la combo perfetta per iniziare a rendere smart la casa I TV 115 pollici si fanno più accessibili: ecco i nuovi QD-Mini LED di TCL

I TV 115 pollici si fanno più accessibili: ecco i nuovi QD-Mini LED di TCL Solo 44 per CMF Watch Pro: lo smartwatch AMOLED che sembra di fascia alta ma costa pochissimo

Solo 44 per CMF Watch Pro: lo smartwatch AMOLED che sembra di fascia alta ma costa pochissimo iPhone 16 Pro e 16 Pro Max sono ancora ai prezzi pazzeschi dei giorni scorsi: ecco la lista dei modelli da valutare

iPhone 16 Pro e 16 Pro Max sono ancora ai prezzi pazzeschi dei giorni scorsi: ecco la lista dei modelli da valutare

2 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoDevi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".