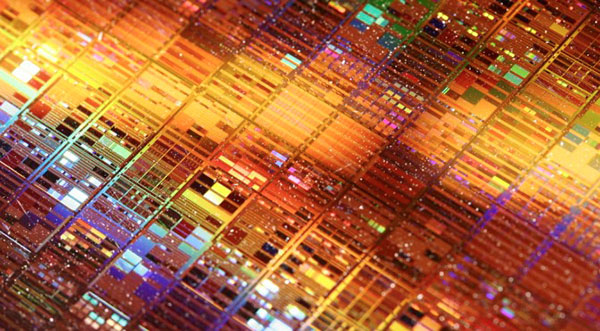

Samsung, la produzione a 3 nanometri slitta a causa del Coronavirus?

Secondo voci industriali, Samsung sarebbe costretta a rimandare la produzione in volumi a 3 nanometri dal 2021 al 2022 a causa dei ritardi nelle consegne dei macchinari necessari alla realizzazione dei chip.

di Manolo De Agostini pubblicata il 07 Aprile 2020, alle 10:01 nel canale ProcessoriSamsung

Secondo indiscrezioni riportate dal Digitimes, Samsung potrebbe essere costretta a rimandare il debutto del processo produttivo a 3 nanometri dal 2021 al 2022. La causa del ritardo sarebbe legata al Coronavirus e all'impossibilità di ricevere e completare l'installazione dei macchinari EUV dedicati alle nuove linee di produzione nei tempi previsti.

Ufficialmente la fase di risk production era prevista per la fine di quest'anno, in vista di una produzione in volumi nell'ultima parte del 2021. Tutto finora sembrava andare per il verso giusto, tanto che a inizio anno l'azienda disse alla stampa locale di aver creato con successo i primi prototipi di chip con il nuovo processo.

È chiaro però che in assenza della giusta quantità di macchinari e linee produttive, Samsung non sarebbe in grado di soddisfare un'eventuale produzione in volumi.

L'obiettivo conclamato dell'azienda asiatica è quello di battere la taiwanese TSMC nella corsa ai 3 nanometri e diventare il primo produttore di semiconduttori al mondo entro il 2030. Un debutto nel 2021 le avrebbe permesso di fare un importante passo avanti verso tale traguardo, mentre il presunto slittamento la metterebbe pressoché in pari con la concorrente.

Per Samsung i 3 nanometri sembrano uno snodo cruciale perché rappresentano il passaggio dei transistor dal progetto FinFET (Fin Field-effect) al Gate All Around FET (GAAFET), che nella sua implementazione prende il nome di MBCFET, Multi Bridge Channel FET.

Samsung lavora ai transistor MBCFET dal 2002 con l'obiettivo di andare oltre le capacità dei transistor FinFET. Per farlo l'azienda aumenterà l'area di contatto tra canale e gate, assicurando che il gate "prosegua" anche sotto il canale, non solo sopra e ai lati. In questo modo Samsung potrà impilare i transistor verticalmente anziché lateralmente e avrà la libertà di implementare diversi form factor.

Leggi anche: TSMC: 7 nanometri non sono 7 nanometri, bisogna trovare nuovi nomi

Il colosso asiatico, stando a quanto noto, punta a implementare il canale come un foglio orizzontale, aumentandone il volume e ottenendo vantaggi sia per quanto concerne le prestazioni che lo scaling. Ed è da questa scelta di design che è nato il design Multi-Bridge Channel FET, un progetto estremamente personalizzabile, che agendo sull'ampiezza del nanofoglio (nanosheet) permette di intervenire su consumi e prestazioni, adattando quindi il design a seconda del mercato.

Con i 3 nanometri, Samsung vuole garantire il 35% di prestazioni in più, consumi inferiori del 50% e un'area del die minore del 45% rispetto ai 7 nanometri.

La rivoluzione dei dati in tempo reale è in arrivo. Un assaggio a Confluent Current 2025

La rivoluzione dei dati in tempo reale è in arrivo. Un assaggio a Confluent Current 2025 SAP Sapphire 2025: con Joule l'intelligenza artificiale guida app, dati e decisioni

SAP Sapphire 2025: con Joule l'intelligenza artificiale guida app, dati e decisioni Dalle radio a transistor ai Micro LED: il viaggio di Hisense da Qingdao al mondo intero

Dalle radio a transistor ai Micro LED: il viaggio di Hisense da Qingdao al mondo intero One UI 7, non vi piacciono alcune novità? Ecco due modifiche che potete annullare

One UI 7, non vi piacciono alcune novità? Ecco due modifiche che potete annullare HUAWEI Pura 80, è ufficiale: la nuova serie flagship sarà lanciata l'11 giugno in Cina

HUAWEI Pura 80, è ufficiale: la nuova serie flagship sarà lanciata l'11 giugno in Cina Meta, i moderatori umani potrebbero essere sostituiti da sistemi AI più efficaci

Meta, i moderatori umani potrebbero essere sostituiti da sistemi AI più efficaci Offerte Notebook: 4 modelli in sconto su Amazon a partire da un ottimo portatile Lenovo da 439

Offerte Notebook: 4 modelli in sconto su Amazon a partire da un ottimo portatile Lenovo da 439 Dreame L40 Ultra scende di altri 100! Allo stesso prezzo c'è anche il modello AE, ecco le differenze introvabili sul web

Dreame L40 Ultra scende di altri 100! Allo stesso prezzo c'è anche il modello AE, ecco le differenze introvabili sul web Windows 11, nuova patch di emergenza KB5062170 per risolvere gli errori di avvio

Windows 11, nuova patch di emergenza KB5062170 per risolvere gli errori di avvio 'Napalm Girl': 400 fotografi contro la decisione del WPP di sospendere la paternità di Nick Ut

'Napalm Girl': 400 fotografi contro la decisione del WPP di sospendere la paternità di Nick Ut Gli italiani ce l'hanno più piccolo della media europea (il televisore)

Gli italiani ce l'hanno più piccolo della media europea (il televisore) Google Maps cambia logo nell'interfaccia mobile: ecco la piccola novità

Google Maps cambia logo nell'interfaccia mobile: ecco la piccola novità Windows 11 in calo a maggio, mentre cresce Windows 10 che a ottobre non sarà più supportato

Windows 11 in calo a maggio, mentre cresce Windows 10 che a ottobre non sarà più supportato Qual è lo smartphone più venduto in Europa? La TOP 10 è dominata due marchi

Qual è lo smartphone più venduto in Europa? La TOP 10 è dominata due marchi ECOVACS DEEBOT T50 PRO OMNI: il robot aspirapolvere da 15.000 Pa con lavaggio ad acqua calda è in offerta su Amazon a soli 699

ECOVACS DEEBOT T50 PRO OMNI: il robot aspirapolvere da 15.000 Pa con lavaggio ad acqua calda è in offerta su Amazon a soli 699 Apple Watch: tutte le offerte su Amazon a Giugno! Series 10 da 46mm a soli 359, sconti anche su Series 9 e SE

Apple Watch: tutte le offerte su Amazon a Giugno! Series 10 da 46mm a soli 359, sconti anche su Series 9 e SE La Via Lattea e la galassia di Andromeda potrebbero non scontrarsi secondo nuovi dati di Hubble e Gaia

La Via Lattea e la galassia di Andromeda potrebbero non scontrarsi secondo nuovi dati di Hubble e Gaia

0 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoDevi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".