Intel PUMA: 8 core e 528 thread, prove tecniche di fotonica del silicio

Da tempo Intel sta lavorando alle interconnessioni ottiche tra chip. A Hot Chips 2023 la casa di Santa Clara ha parlato di PUMA, un prototipo di chip che conta 8 core e 528 thread, ed è capace di un throughput ottico fino a 1 TB/s.

di Manolo De Agostini pubblicata il 31 Agosto 2023, alle 13:41 nel canale ProcessoriIntel

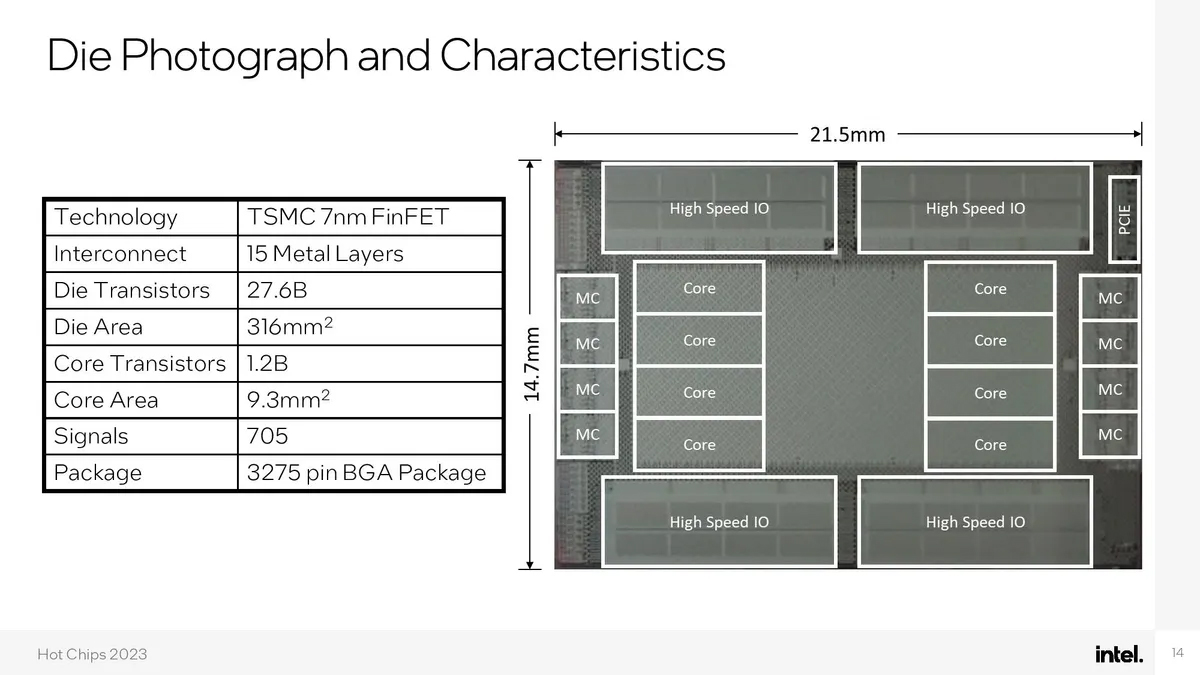

Durante Hot Chips 2023 Intel ha dimostrato i progressi che sta compiendo nell'ambito delle interconnessioni tra chip mediante soluzioni ottiche. Per la sua dimostrazione, la casa di Santa Clara ha usato un chip molto particolare, ribattezzato PUMA (Programmable Unified Memory Architecture), basato su un'architettura RISC custom. Il chip è stato sviluppato all'interno del programma DARPA HIVE ed è stato prodotto da TSMC a 7 nanometri.

A colpire in modo particolare è che si tratta di un chip con 8 core e 528 thread, ossia ben 66 thread per core per un throughput ottico fino a 1 TB/s. Un altro aspetto interessante è che questo chip consuma solo 75W, di cui circa il 60% è legato alle interconnessioni ottiche.

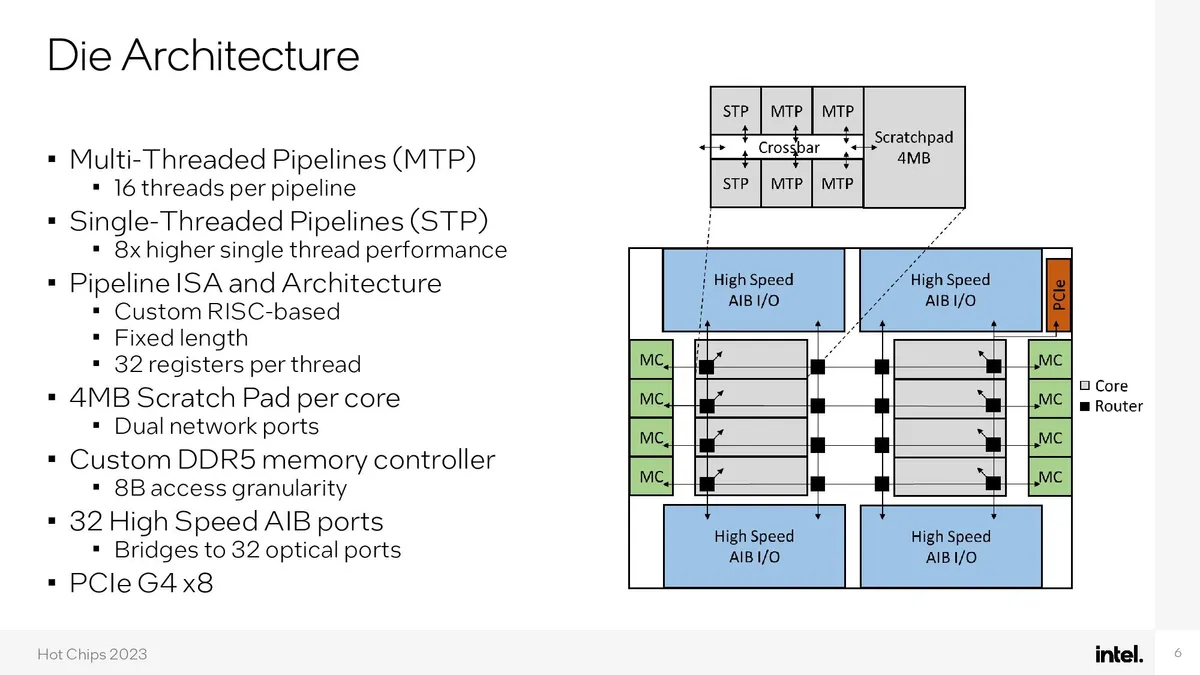

L'uso dell'architettura RISC - ricordiamo che Intel è la regina dell'x86 - assicura secondo la società prestazioni ottimizzate nei carichi di lavoro di analisi dei grafi, garantendo un miglioramento delle prestazioni single-thread di 8 volte.

Il core personalizzato di Intel, oltre a supportare 66 thread, prevede 192 KB di cache L1 instruction e dati e 4 MB di SRAM per core. Il chip a otto core presenta 32 porte I/O ottiche che operano a 32 GB/s/dir ciascuna, per una bandwidth totale di 1 TB/s. I chip vengono inseriti in una slitta OCP a otto socket, che offre fino a 16 TB/s di throughput ottico totale per il sistema e ciascun chip è alimentato da 32 GB di DRAM DDR5-4000 "custom".

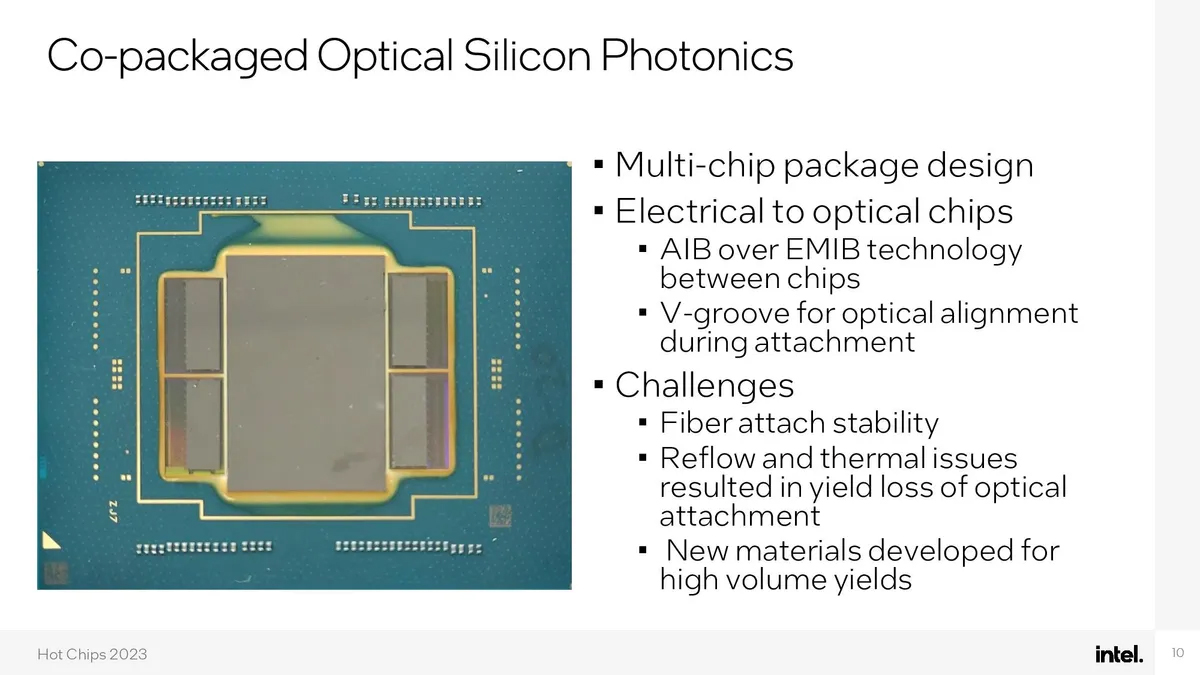

L'intero chip PUMA conta 27,6 miliardi di transistor su un'area di 316 mm2. Gli otto core, che insieme richiedono 1,2 miliardi di transistor, si trovano al centro del die, fiancheggiati da otto controller di memoria ad hoc. Il chip prevede anche quattro chiplet di /O ottici a otto canali ad alta velocità, due ciascuno sopra e sotto il die, necessari a interfacciare i segnali elettrici interni alle interconnessioni ottiche esterne. Queste unità sono connesse mediante tecnologia di packaging EMIB di Intel e usano il protocollo AIB. Il chip ha anche una connessione PCIe 4.0 x8 per comunicare con il resto del sistema.

Al fine di gestire l'enorme quantità di dati generata dai 528 thread nel die, Intel ha progettato una mesh 2D on-die con 16 router per spostare i dati tra core, controller di memoria e interconnessioni fotoniche. I connettori fotonici sono integrati nel package per il collegamento esterno verso altri chip.

Il chip è collegato a una rete ottica esterna "HyperX" che fornisce connessioni "all-to-all" per i singoli core. Questa incredibile rete consente di connettere direttamente fino a 2 milioni di core "all-to-all" con una latenza inferiore a 400 ns.

Il risultato finale è impressionante: il chip consuma solo 75 W, con il 59% del budget dedicato alla fotonica del silicio e il 21% ai core. Intel afferma che le prestazioni della rete ottica consentono uno scaling lineare quasi perfetto da uno fino a 1000 core.

FRITZ!Repeater 1700 estende la rete super-veloce Wi-Fi 7

FRITZ!Repeater 1700 estende la rete super-veloce Wi-Fi 7 Fondazione Chips-IT, l'Italia alla riscossa nei chip. Il piano e la partnership EssilorLuxottica

Fondazione Chips-IT, l'Italia alla riscossa nei chip. Il piano e la partnership EssilorLuxottica Nutanix: innovazione, semplicità e IA al centro della strategia hybrid multicloud

Nutanix: innovazione, semplicità e IA al centro della strategia hybrid multicloud Il futuro dei chip è verticale: RAM e logica impilati per chip più efficienti, ma realizzabili (quasi) ovunque

Il futuro dei chip è verticale: RAM e logica impilati per chip più efficienti, ma realizzabili (quasi) ovunque Accenture e Anthropic insieme per aiutare le imprese a sprigionare il valore dell'IA

Accenture e Anthropic insieme per aiutare le imprese a sprigionare il valore dell'IA Fino a 360 GB su un vetro grande come una moneta: l'archiviazione del futuro presto alla prova dei fatti

Fino a 360 GB su un vetro grande come una moneta: l'archiviazione del futuro presto alla prova dei fatti tado° porta il bilanciamento idraulico automatico nelle case: più efficienza nel riscaldamento senza interventi tecnici

tado° porta il bilanciamento idraulico automatico nelle case: più efficienza nel riscaldamento senza interventi tecnici Metallo liquido o solido? Entrambi, contemporaneamente: lo stato ibrido che sfida la fisica

Metallo liquido o solido? Entrambi, contemporaneamente: lo stato ibrido che sfida la fisica iPhone 17 Pro Max in offerta su Amazon: la versione da 256 GB scende a 1.349

iPhone 17 Pro Max in offerta su Amazon: la versione da 256 GB scende a 1.349 A Taranto divieto di bici, e-bike e monopattini in zone pedonali. Richiesta una revisione

A Taranto divieto di bici, e-bike e monopattini in zone pedonali. Richiesta una revisione  Scopa elettrica lava e aspira come una top di gamma: DREAME H12 Pro FlexReach scende a 229 su Amazon

Scopa elettrica lava e aspira come una top di gamma: DREAME H12 Pro FlexReach scende a 229 su Amazon SumUp continua a crescere ed espande l'offerta

SumUp continua a crescere ed espande l'offerta Volkswagen ID.Polo: da 25.000 euro, in quattro versioni con due batterie

Volkswagen ID.Polo: da 25.000 euro, in quattro versioni con due batterie iPhone Fold: le ultime indiscrezioni suggeriscono l'assenza del Face ID

iPhone Fold: le ultime indiscrezioni suggeriscono l'assenza del Face ID Audi Revolut F1 Team: annunciati nome e logo della nuova squadra del circus

Audi Revolut F1 Team: annunciati nome e logo della nuova squadra del circus Resident Evil - Code Veronica Remake: l'annuncio è atteso per il prossimo anno con uscita nel 2027

Resident Evil - Code Veronica Remake: l'annuncio è atteso per il prossimo anno con uscita nel 2027 Occhio ai prezzi dei robot ECOVACS Deebot: su Amazon si torna ai livelli del Black Friday da 199

Occhio ai prezzi dei robot ECOVACS Deebot: su Amazon si torna ai livelli del Black Friday da 199

6 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoDobbiamo prepararci al peggio!

Dobbiamo prepararci al peggio!

Cosa scommettiamo che è una vaccata enorme?

Dobbiamo prepararci al peggio!

Certo certo, in effetti la Russia sta mostrando avanzamenti tecnologici da paura

Però hanno intercettato 42 renne che hanno attraversato il confine.

https://it.euronews.com/green/2023/...ia-corre-ai-rip

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".