IDF Fall 2008 Day 1: SSD, Nehalem e Larrabee

Primo giorno di apertura ufficiale dell'IDF, Intel Developer Forum, in corso a San Francisco. Una giornata dai toni altalenanti, in cui notizie già note si sono alternate ad altre più interessanti. Fra queste, qualche notizia in più su Larrabee, la microarchitettura tuttofare di Intel, nonché maggiori informazioni sul progetto Nehalem

di Alessandro Bordin , Andrea Bai pubblicato il 20 Agosto 2008 nel canale ProcessoriIntel

Nehalem

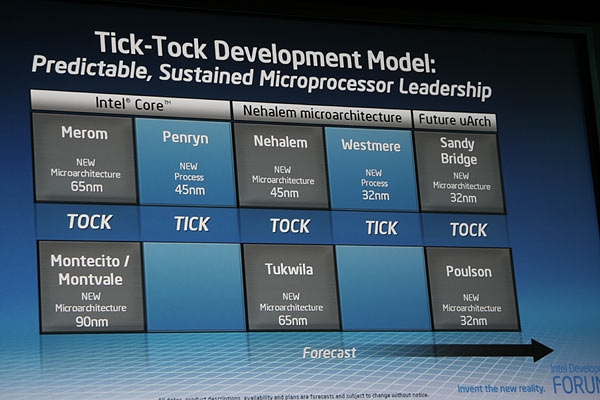

Dopo che l'astratto ha caratterizzato il keynote mattutino e l'avvio di questa sessione pomeridiana, si prende finalmente contatto con qualche informazione più concreta, nella fattispecie riguardante l'architettura Nehalem e le incarnazioni con la quale essa arriverà sul mercato a partire dai prossimi mesi.

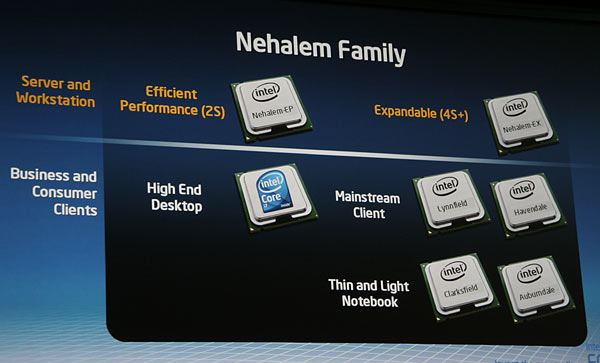

E' il caso di ribadirlo nuovamente: Nehalem è il nome in codice della microarchitettura di nuova generazione sviluppata da Intel dalla quale nasceranno processori destinati all'ambito desktop e server, così come alcune varianti indirizzate anche ai segmenti mobile, per la prossima piattaforma destinata ai sistemi portatili e conosciuta con il nome in codice di Calpella. Pat Gelsinger, con l'aiuto di Rajesh Kumar, ha illustrato alcune nuove caratteristiche dell'architettura Nehalem, che si vanno ad aggiungere alle informazioni già note da tempo e che potete trovare raccolte in questo articolo.

Particolare sottolineatura alle caratteristiche Power Gates e Turbo Mode. La

prima consente di ridurre il consumo energetico grazie alla possibilità di

disattivare completamente i core del processore in modo indipendente l'uno

dall'altro e, altrettanto indipendentemente, di regolarne frequenza e tensione

operative. La riduzione dei consumi è possibile grazie anche ad una particolare

progettazione del chip che consente di contenere considerevolmente la

dispersione di corrente (leakage).

Turbo Mode (che non richiede interventi da parte del sistema operativo)

permette invece di operare anche su un singolo core una sorta di overclock a più

stadi. Qualora le applicazioni in esecuzione non fossero studiate per operare

con CPU multi-core o con un numero di core inferiore a quelli di Nehalem, si

potrà contare su un aumento della frequenza dei o del core utilizzato.

Il lavoro svolto da Power Gates e Turbo Mode è molto interessante quando operano in contemporanea. In presenza di applicativi che non sfruttano tutti i core, infatti, la tecnologia Power Gates provvederà a portare i core inutilizzati allo stadio di consumo energetico C6, in pratica quasi spenti del tutto. Nel frattempo la tecnologia Turbo Mode aumenterà la frequenza del o dei core realmente utilizzati, con un duplice vantaggo. Da una parte il maggiore consumo dei core overcloccati è pienamente compensato dalla disattivazione di quelli utilizzati; dall'altro, la maggiore frequenza operativa garantirà al contempo prestazioni superiori rispetto a processori sempre multi-core ma non in grado di adattarsi in modo intelligente alle esigenze di sistema. Ne consegue, per Nehalem, un consumo inferiore abbinato a prestazioni migliori negli scenari finora descritti, decisamente frequenti allo stato attuale delle cose.

Come già noto da qualche tempo, il nome commerciale del primo prodotto desktop basato sull'architettura Nehalem sarà Core i7. Pat Gelsinger ha confermato che Core i7 arriverà sul mercato entro la fine dell'anno, assieme ad un processore destinato al segmento server, in particolare per le soluzioni efficient performance, e che sarà basato su una versione di core attualmente conosciuta con il nome in corice di "Nehalem-EP".

Sarà tuttavia nel corso del 2009 che il mercato inizierà ad affollarsi, in tutti i suoi segmenti, di soluzioni derivate dalla nuova architettura: sul fronte expandable server avremo Nehalem-EX, sul versante desktop Intel proporrà le due varianti "Havendale" e "Lynnfield" mentre invece le soluzioni mobile saranno rappresentate da "Auburndale" e "Clarksfield".

Si è parlato, all'esordio di Nehalem, di versioni fino ad 8 core. Proprio

nella giornata di oggi Pat Gelsinger ha mostrato con orgoglio il primo

wafer di questi chip che, grazie alla tecnologia Hyper-Threading, verranno

riconosciuti dal sistema come 16 unità logiche.

La rivoluzione dei dati in tempo reale è in arrivo. Un assaggio a Confluent Current 2025

La rivoluzione dei dati in tempo reale è in arrivo. Un assaggio a Confluent Current 2025 SAP Sapphire 2025: con Joule l'intelligenza artificiale guida app, dati e decisioni

SAP Sapphire 2025: con Joule l'intelligenza artificiale guida app, dati e decisioni Dalle radio a transistor ai Micro LED: il viaggio di Hisense da Qingdao al mondo intero

Dalle radio a transistor ai Micro LED: il viaggio di Hisense da Qingdao al mondo intero ASRock ammette i problemi del BIOS, ma pare che non si assumerà la responsabilità per le CPU danneggiate

ASRock ammette i problemi del BIOS, ma pare che non si assumerà la responsabilità per le CPU danneggiate Elon Musk annuncia i nuovi piani per la colonizzazione di Marte grazie a SpaceX Starship

Elon Musk annuncia i nuovi piani per la colonizzazione di Marte grazie a SpaceX Starship Mafia: The Old Country in azione in un video commentato dagli sviluppatori

Mafia: The Old Country in azione in un video commentato dagli sviluppatori Pulizie automatiche e senza grovigli: Roborock QV 35A è oggi in sconto super, ecco come comprarlo a 474

Pulizie automatiche e senza grovigli: Roborock QV 35A è oggi in sconto super, ecco come comprarlo a 474 Cybersecurity: così CrowdStrike protegge l'AI Factory di NVIDIA

Cybersecurity: così CrowdStrike protegge l'AI Factory di NVIDIA Rotterdam mette alla prova Artemis EF-12: prima imbarcazione elettrica per pattugliamento entra in servizio

Rotterdam mette alla prova Artemis EF-12: prima imbarcazione elettrica per pattugliamento entra in servizio MSI MPG X870I Edge TI WiFi: la motherboard ITX che si sente una E-ATX

MSI MPG X870I Edge TI WiFi: la motherboard ITX che si sente una E-ATX Download.it salva FilePlanet: oltre 120.000 file storici del gaming tornano online

Download.it salva FilePlanet: oltre 120.000 file storici del gaming tornano online WhatsApp sta per introdurre gli username: addio al numero di telefono visibile

WhatsApp sta per introdurre gli username: addio al numero di telefono visibile Successo per il primo test della PEC europea tra Aruba e Asseco

Successo per il primo test della PEC europea tra Aruba e Asseco Cosa cambia con la partnership fra Pure Storage e Nutanix? Ce lo spiega Maciej Kranz, General Manager, Enterprise di Pure Storage

Cosa cambia con la partnership fra Pure Storage e Nutanix? Ce lo spiega Maciej Kranz, General Manager, Enterprise di Pure Storage Sony abbandona la produzione interna degli smartphone: cosa cambia per gli utenti Xperia?

Sony abbandona la produzione interna degli smartphone: cosa cambia per gli utenti Xperia? Il futuro degli aerei elettrici passa per il sodio: il MIT svela una fuel cell tre volte più efficiente delle batterie agli ioni di litio

Il futuro degli aerei elettrici passa per il sodio: il MIT svela una fuel cell tre volte più efficiente delle batterie agli ioni di litio Sentenza blocca i dazi di Trump: "Il Presidente ha superato i suoi poteri". Ma per poco

Sentenza blocca i dazi di Trump: "Il Presidente ha superato i suoi poteri". Ma per poco