Zen 5 e Zen 6: presunti dettagli sulle future architetture AMD trapelano online

In rete trapelano presunti dettagli sulle architetture AMD Zen 5 e Zen 6, dai nomi in codice al miglioramento in termini di IPC, fino ad arrivare al numero di core per CCD. Informazioni che fanno riferimento, però, a una roadmap non recente.

di Manolo De Agostini pubblicata il 29 Settembre 2023, alle 12:51 nel canale ProcessoriAMDRyzenZenThreadripperEPYC

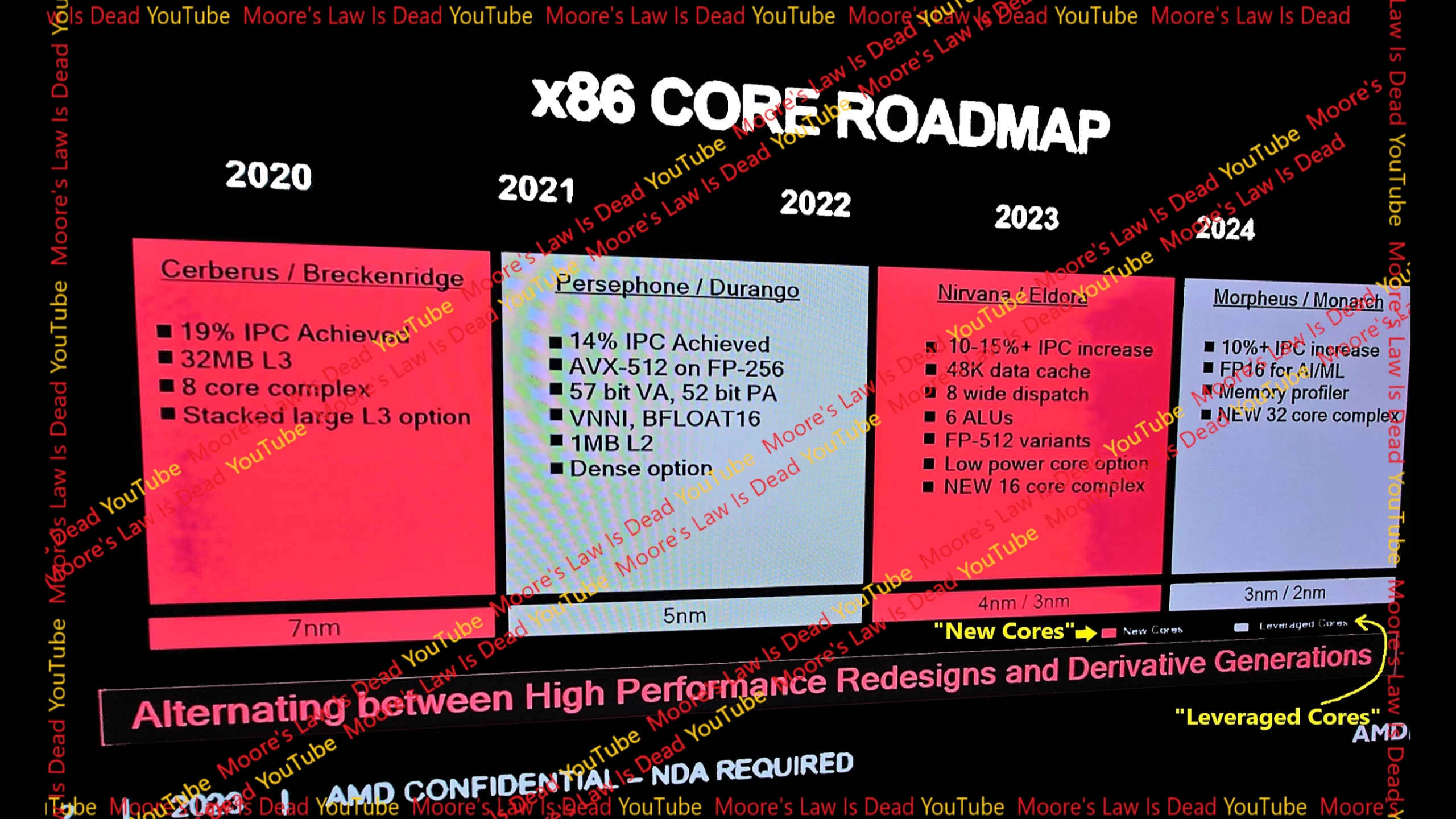

Il leaker Moore's Law Is Dead ha pubblicato in un video una roadmap relativa all'architettura Zen di AMD, in particolare le future iterazioni Zen 5 e Zen 6. Va precisato subito che la roadmap mostrata non sembra essere aggiornatissima, di fatti Zen 5 è incasellato per il 2023 ma sappiamo che i processori arriveranno sul mercato non prima del 2024. Ciononostante, la roadmap può essere indicativa sulle aspirazioni e la direzione intrapresa da AMD.

Per prima cosa, è bene spiegare i nomi in codice che si vedono: Cerberus è il nome in codice del progetto Zen 3, mentre Breckenridge è il nome dato internamente al corrispettivo CCD. Vediamo poi Persephone (architettura) e Durango (CCD) per Zen 4, seguiti da Nirvana (architettura) ed Eldora (CCD) per quanto riguarda Zen 5 e, infine, Morpheus (architettura) e Monarch (CCD) per la generazione Zen 6.

Con Zen 5 AMD sembra voglia raddoppiare il numero di core nel CCD, salendo a 16 come ha fatto con Zen 4c, mentre il CCD di Zen 4 ne offre solo 8. Oggi confezionare un processore con 16 core su desktop richiede due CCD, mentre con Zen 5 raggiungere quel numero potrebbe richiedere un solo CCD.

Nella slide si parla però di un'opzione per "core a basso consumo". Cosa potrebbe significare? Difficile dirlo, ma forse che non cambierà nulla rispetto a quanto visto con Zen 4 e Zen 4c: il CCD di Zen 5 potrebbe avere 8 core come quello di Zen 4, mentre quello di Zen 5c ben 16 come Zen 4c. In passato si è vociferato che i Ryzen 8000 desktop non avranno più core dei modelli 7000, quindi l'ipotesi appare probabile.

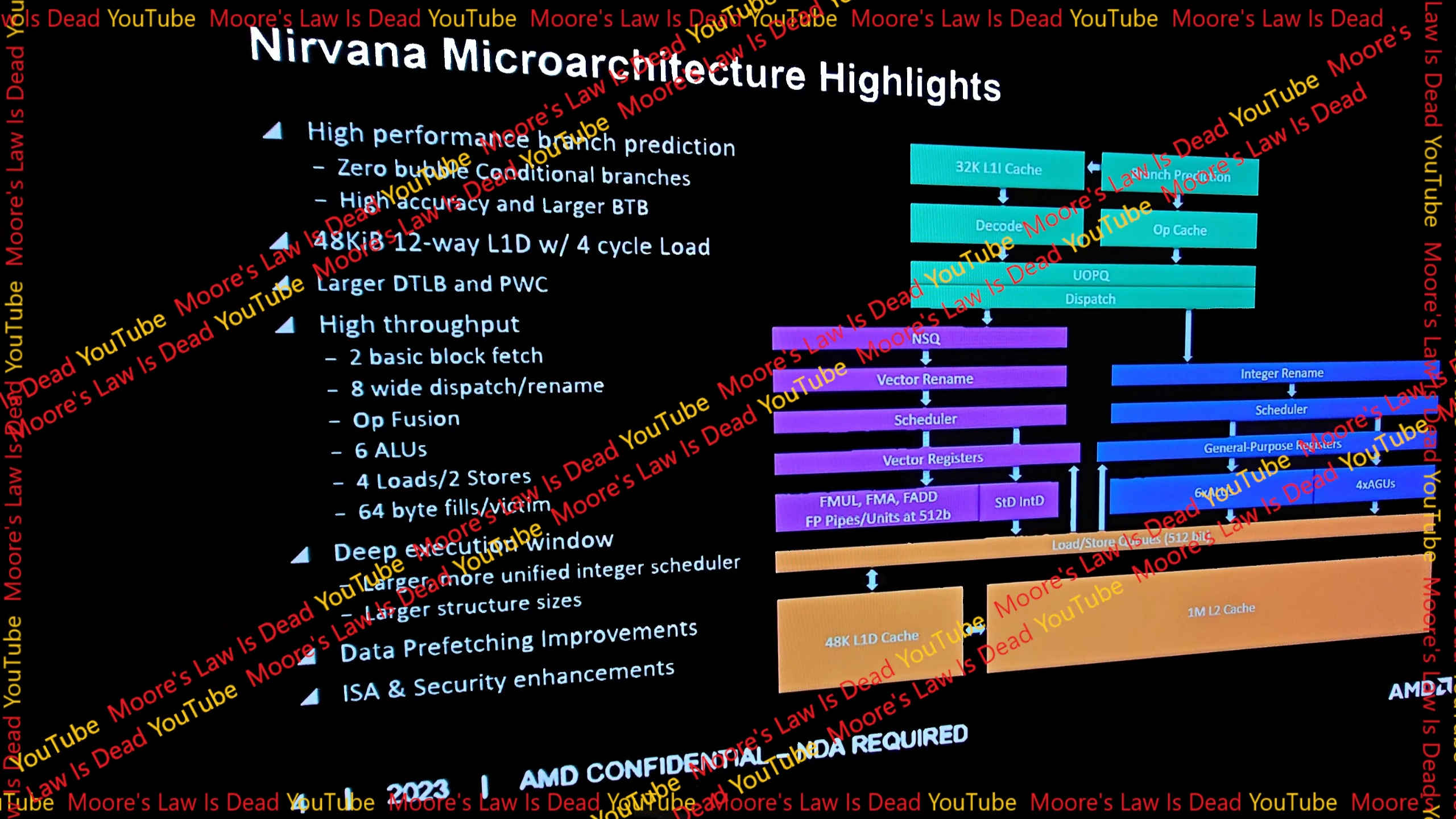

AMD prevede un aumento dell'IPC dal 10 al 15% per Zen 5. Un balzo figlio di diversi interventi sulla microarchitettura come l'espansione della cache L1 dati a 48 kB (32 kB su Zen 4) e l'aumento delle ALU (Arithmetic Logic Unit) portandole dalle quattro di Zen 4 alle sei di Zen 5. Il progetto sarà anche in grado di "digerire" il formato dati FP-512 in alcune varianti. I CCD di Zen 5 saranno prodotti con processi a 4 e/o 3 nanometri, ma dato che la roadmap non è dell'ultimo periodo, questa informazione va presa con cautela.

Come si evince passando a Zen 6, infatti, AMD era ottimista di poter produrre il CCD a 3 e/o 2 nanometri, ma molto dipenderà dalle risorse di TSMC. Per Zen 6 AMD auspicherebbe un aumento dell'IPC del 10% e il supporto al formato FP-16 per accelerare le applicazioni ML/AI.

La roadmap, inoltre, parla anche di un Core Complex con un massimo di 32 core. Anche in questo caso per ora sembra un numero legato all'implementazione Zen 6c.

Per quanto concerne il packaging, Zen 5 avrà probabilmente una struttura simile agli attuali processori Ryzen ed EPYC, con l'I/O die posizionato accanto ai CCD e un packaging basato su tecnologie 2.5D.

Con Zen 6 ci sarà un cambiamento importante, con i CCD posizionati sull'I/O die, una soluzione definita come "die stacking". In tal senso bisognerà capire se la 3D V-Cache continuerà a esistere, se sarà impilata sempre sul CCD o se cambierà di posizione.

BOOX Note Air4 C è uno spettacolo: il tablet E Ink con Android per lettura e scrittura

BOOX Note Air4 C è uno spettacolo: il tablet E Ink con Android per lettura e scrittura Recensione Sony Xperia 1 VII: lo smartphone per gli appassionati di fotografia

Recensione Sony Xperia 1 VII: lo smartphone per gli appassionati di fotografia Attenti a Poco F7: può essere il best buy del 2025. Recensione

Attenti a Poco F7: può essere il best buy del 2025. Recensione Auto nuove? Per il 65% degli italiani sono troppo care, non dovrebbero costare oltre i 20.000 euro

Auto nuove? Per il 65% degli italiani sono troppo care, non dovrebbero costare oltre i 20.000 euro Droni solari Airbus volano nella stratosfera grazie alle nuove batterie al silicio: test riusciti a oltre 20 km di quota

Droni solari Airbus volano nella stratosfera grazie alle nuove batterie al silicio: test riusciti a oltre 20 km di quota Colpo da 15 milioni di dollari: chi ha rubato un carico di prodotti AMD e Apple?

Colpo da 15 milioni di dollari: chi ha rubato un carico di prodotti AMD e Apple? Elon Musk lancia l'allarme su GPT-5: 'OpenAI divorerà Microsoft'. Ma Nadella lo sfida con un sorriso

Elon Musk lancia l'allarme su GPT-5: 'OpenAI divorerà Microsoft'. Ma Nadella lo sfida con un sorriso iPhone 17 Pro sarà più costoso, ma anche più conveniente

iPhone 17 Pro sarà più costoso, ma anche più conveniente Leapmotor spinge sull'acceleratore: nuovo C10 AWD da 585 cavalli e ricarica ultraveloce a 800V

Leapmotor spinge sull'acceleratore: nuovo C10 AWD da 585 cavalli e ricarica ultraveloce a 800V Toyota vuole battere i produttori cinesi di auto elettriche. Come? Alleandosi con i loro fornitori

Toyota vuole battere i produttori cinesi di auto elettriche. Come? Alleandosi con i loro fornitori Colpo grosso di Musk: 14 ricercatori Meta hanno scelto xAI per il futuro dell'AI

Colpo grosso di Musk: 14 ricercatori Meta hanno scelto xAI per il futuro dell'AI Lip-Bu Tan a testa alta: il CEO di Intel non ha paura di Trump

Lip-Bu Tan a testa alta: il CEO di Intel non ha paura di Trump GPT5 disponibile per tutti e puoi già usarlo: offre Microsoft!

GPT5 disponibile per tutti e puoi già usarlo: offre Microsoft! Nasce l'alternativa a Worldcoin: Humanity Protocol lancia una rete da 1,1 miliardi di dollari per dare un'identità Web3 senza scanner dell'iride

Nasce l'alternativa a Worldcoin: Humanity Protocol lancia una rete da 1,1 miliardi di dollari per dare un'identità Web3 senza scanner dell'iride ASUSTOR presenta i nuovi NAS da rack Lockerstor R Pro Gen2 con CPU AMD Ryzen Pro

ASUSTOR presenta i nuovi NAS da rack Lockerstor R Pro Gen2 con CPU AMD Ryzen Pro iPhone 18, sensori Samsung realizzati in Texas: gli effetti dei dazi amari di Trump sui semiconduttori

iPhone 18, sensori Samsung realizzati in Texas: gli effetti dei dazi amari di Trump sui semiconduttori Xiaomi conquista il terzo posto nel mercato italiano: è l'unica in crescita nella Top5

Xiaomi conquista il terzo posto nel mercato italiano: è l'unica in crescita nella Top5

1 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoDevi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".