TSMC, dai wafer rotondi a quelli rettangolari per produrre molti più chip?

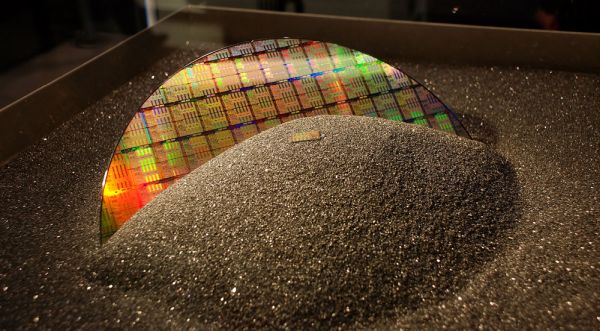

Secondo il giapponese Nikkei, TSMC starebbe sviluppando un nuovo metodo di packaging basato substrati rettangolari simili a pannelli al posto dei tradizionali wafer rotondi da 300 mm. Lo studio sarebbe solo agli inizi, per una novità che richiederebbe drastici cambiamenti nella filiera produttiva dei semiconduttori.

di Manolo De Agostini pubblicata il 21 Giugno 2024, alle 13:41 nel canale ProcessoriTSMC

Secondo quanto riportato dal quotidiano giapponese Nikkei, TSMC starebbe sviluppando un nuovo metodo avanzato di packaging dei chip basato su substrati rettangolari simili a pannelli per soddisfare la crescente domanda di soluzioni multi-chiplet.

Lo sviluppo sarebbe ancora nelle fasi iniziali e potrebbe richiedere diversi anni per vedere un'applicazione concreta. Invece di wafer di 300 mm di diametro, il nuovo metodo di TSMC utilizzerebbe substrati rettangolari da 510 x 515 mm.

L'obiettivo è quello di avere un'area utilizzabile circa 3,7 volte più grande dei tradizionali wafer rotondi da 300 mm, in modo da di produrre più chip per wafer e avere meno scarti ai bordi. Inoltre, si potrebbero realizzare interposer di dimensioni più grandi.

C'è un problema: il nuovo metodo richiede macchinari totalmente nuovi, differenti da quelli usati attualmente. A tal fine, TSMC starebbe lavorando con i fornitori di macchinari e materiali su questa nuova tecnologia di packaging, ma al momento non ci sono altri dettagli.

L'azienda ha risposto al Nikkei spiegando che sta monitorando da vicino i progressi nelle tecnologie di packaging avanzate, compreso il packaging descritto, senza elaborare ulteriormente.

In passato si pensò di realizzare wafer di diametro maggiore, da 450 mm, in modo da aumentare notevolmente il numero di chip per wafer. Poi, però, la spinta verso quella direzione si affievolì, con il rallentamento della Legge di Moore e la necessità di aggiornare, comunque, i macchinari produttivi e le Fab. Insomma, i conti non tornavano.

BOOX Note Air4 C è uno spettacolo: il tablet E Ink con Android per lettura e scrittura

BOOX Note Air4 C è uno spettacolo: il tablet E Ink con Android per lettura e scrittura Recensione Sony Xperia 1 VII: lo smartphone per gli appassionati di fotografia

Recensione Sony Xperia 1 VII: lo smartphone per gli appassionati di fotografia Attenti a Poco F7: può essere il best buy del 2025. Recensione

Attenti a Poco F7: può essere il best buy del 2025. Recensione Droni solari Airbus volano nella stratosfera grazie alle nuove batterie al silicio: test riusciti a oltre 20 km di quota

Droni solari Airbus volano nella stratosfera grazie alle nuove batterie al silicio: test riusciti a oltre 20 km di quota Colpo da 15 milioni di dollari: chi ha rubato un carico di prodotti AMD e Apple?

Colpo da 15 milioni di dollari: chi ha rubato un carico di prodotti AMD e Apple? Elon Musk lancia l'allarme su GPT-5: 'OpenAI divorerà Microsoft'. Ma Nadella lo sfida con un sorriso

Elon Musk lancia l'allarme su GPT-5: 'OpenAI divorerà Microsoft'. Ma Nadella lo sfida con un sorriso iPhone 17 Pro sarà più costoso, ma anche più conveniente

iPhone 17 Pro sarà più costoso, ma anche più conveniente Leapmotor spinge sull'acceleratore: nuovo C10 AWD da 585 cavalli e ricarica ultraveloce a 800V

Leapmotor spinge sull'acceleratore: nuovo C10 AWD da 585 cavalli e ricarica ultraveloce a 800V Toyota vuole battere i produttori cinesi di auto elettriche. Come? Alleandosi con i loro fornitori

Toyota vuole battere i produttori cinesi di auto elettriche. Come? Alleandosi con i loro fornitori Colpo grosso di Musk: 14 ricercatori Meta hanno scelto xAI per il futuro dell'AI

Colpo grosso di Musk: 14 ricercatori Meta hanno scelto xAI per il futuro dell'AI Lip-Bu Tan a testa alta: il CEO di Intel non ha paura di Trump

Lip-Bu Tan a testa alta: il CEO di Intel non ha paura di Trump GPT5 disponibile per tutti e puoi già usarlo: offre Microsoft!

GPT5 disponibile per tutti e puoi già usarlo: offre Microsoft! Nasce l'alternativa a Worldcoin: Humanity Protocol lancia una rete da 1,1 miliardi di dollari per dare un'identità Web3 senza scanner dell'iride

Nasce l'alternativa a Worldcoin: Humanity Protocol lancia una rete da 1,1 miliardi di dollari per dare un'identità Web3 senza scanner dell'iride ASUSTOR presenta i nuovi NAS da rack Lockerstor R Pro Gen2 con CPU AMD Ryzen Pro

ASUSTOR presenta i nuovi NAS da rack Lockerstor R Pro Gen2 con CPU AMD Ryzen Pro iPhone 18, sensori Samsung realizzati in Texas: gli effetti dei dazi amari di Trump sui semiconduttori

iPhone 18, sensori Samsung realizzati in Texas: gli effetti dei dazi amari di Trump sui semiconduttori Xiaomi conquista il terzo posto nel mercato italiano: è l'unica in crescita nella Top5

Xiaomi conquista il terzo posto nel mercato italiano: è l'unica in crescita nella Top5 Pulizia millimetrica senza muovere un dito: DJI combina droni e robot aspirapolvere

Pulizia millimetrica senza muovere un dito: DJI combina droni e robot aspirapolvere

12 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoSecondo il giapponese Nikkei, TSMC starebbe sviluppando un nuovo metodo di packaging basato substrati rettangolari simili a pannelli al posto dei tradizionali wafer rotondi da 300 mm. Lo studio sarebbe solo agli inizi, per una novità che richiederebbe drastici cambiamenti nella filiera produttiva dei semiconduttori.

Click sul link per visualizzare la notizia.

certo che fare chip rettangolari su wafer rotondi non è molto efficiente...

non esistono alternative a questo

i chip devono essere rettangolari? non mi risulta

interessante

Non, non devono essere rettangolari. Ma:

[LIST=1]

[*]Devono evitare di sprecare spazio del wafer, per cui è bene far riferimento a una tassellatura del piano.

[*]Dato che in genere su un wafer si producono tutti chip uguali, la tassellatura deve essere basata su un unico poligono ripetuto.

[/LIST]

Dati questi requisiti, per quanto noto (ci sono ricerche in ambito matematico), le tassellature possibili sono quattro, di cui tre regolari (ovvero i tasselli si ripetono in maniera periodica):

[LIST=1]

[*]Tassellatura regolare triangolare (per esempio un triangolo rettangolo isoscele o un triangolo equilatero)

[*]Tassellatura regolare quadrangolare (per esempio un rettangolo o un quadrato)

[*]Tassellatura regolare esagonale (per esempio un esagono regolare)

[*]https://www.sciencenews.org/article/mathematicians-discovered-einstein-tile"]Tassellatura non regolare basata su una sola pietra (ein Stein in tedesco)[/URL]

[/LIST]

Volendo semplificare la progettazione del chip e le sue relazioni con i componenti adiacenti, quale soluzione viene naturale?

È come chiedersi perché le case sono progettate con angoli retti. Pensa alla complicazione di arredare una stanza circolare od ovale: devi far fare solo mobili su misura, e le stanze adiacenti avranno delle forme strane.

e quindi evitare il "mascheraggio" ultra(edit+foto)litografico alle zone ai bordi (mi è ignoto se possa essere più costoso)

devo fare interrogativo per una consulenza dell' ASML, ciò al fine di ottimizzare la loro produzione

[LIST=1]

[*]Devono evitare di sprecare spazio del wafer, per cui è bene far riferimento a una tassellatura del piano.

[*]Dato che in genere su un wafer si producono tutti chip uguali, la tassellatura deve essere basata su un unico poligono ripetuto.

[/LIST]

Dati questi requisiti, per quanto noto (ci sono ricerche in ambito matematico), le tassellature possibili sono quattro, di cui tre regolari (ovvero i tasselli si ripetono in maniera periodica):

[LIST=1]

[*]Tassellatura regolare triangolare (per esempio un triangolo rettangolo isoscele o un triangolo equilatero)

[*]Tassellatura regolare quadrangolare (per esempio un rettangolo o un quadrato)

[*]Tassellatura regolare esagonale (per esempio un esagono regolare)

[*]https://www.sciencenews.org/article/mathematicians-discovered-einstein-tile"]Tassellatura non regolare basata su una sola pietra (ein Stein in tedesco)[/URL]

[/LIST]

Volendo semplificare la progettazione del chip e le sue relazioni con i componenti adiacenti, quale soluzione viene naturale?

È come chiedersi perché le case sono progettate con angoli retti. Pensa alla complicazione di arredare una stanza circolare od ovale: devi far fare solo mobili su misura, e le stanze adiacenti avranno delle forme strane.

l'esagono su wafer esagonale fa così schifo?...

interessante

https://youtu.be/2qLI-NYdLy8?feature=shared

Link ad immagine (click per visualizzarla)

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".