Architettura Zen 3: tutte le novità dei Ryzen 5000 su desktop e mobile

Con l'annuncio delle nuove APU mobile Ryzen 5000 "Cezanne" AMD ha completato la transizione all'architettura Zen 3 nel settore consumer. Vediamo insieme le novità di questa architettura che hanno permesso ad AMD di tornare al vertice delle prestazioni nel gaming e rafforzare ulteriormente la sua posizione con carichi multi-thread.

di Manolo De Agostini pubblicato il 24 Febbraio 2021 nel canale ProcessoriAMDRyzenZen

AMD ha introdotto i microprocessori basati su architettura Zen 3 sul finire dello scorso anno in ambito desktop e all'inizio del 2021 ha portato la medesima architettura anche nel settore mobile. Abbiamo provato le nuove CPU desktop (qui e qui), dandovi un'infarinatura sui punti di forza delle nuove soluzioni, ma l'approdo in ambito mobile consente di dare uno sguardo totale a Zen 3 cogliendo l'essenza del lavoro fatto dall'azienda statunitense.

Con Zen 3, AMD si è mossa su tre direttive principali: prestazioni, latenza ed efficienza. Provando i microprocessori desktop abbiamo ravvisato, numeri alla mano, un forte incremento delle prestazioni multi-thread e, allo stesso tempo, un marcato passo avanti per quanto concerne i calcoli single-thread, con riflessi importanti nel mondo del gaming.

I processori Ryzen 5000 desktop e mobile conservano lo stesso numero di core e thread della serie precedente, quindi nel settore desktop arriviamo fino a 16 core e 32 thread, mentre in ambito mobile ci si ferma a 8 core e 16 thread, mantenendo come espressione massima il rapporto 1 core / 2 thread. Non ci sono novità sotto questo punto di vista, e non si può certo condannare la scelta di AMD, in quanto l'uso dei core deve essere alimentato dalla piattaforma e dal software: non avrebbe senso salire con il numero di thread senza un'applicazione concreta. Aumentare il numero di core, inoltre, avrebbe comportato ulteriori difficoltà in base di progettazione che avrebbero potuto dilatare le tempistiche di arrivo sul mercato delle nuove CPU / APU.

Un altro elemento in comune tra i processori Ryzen 5000 desktop e mobile è l'uso del processo produttivo a 7 nanometri di TSMC, ulteriormente migliorato rispetto ai Ryzen 3000 (desktop) / 4000 (mobile) per far sì che a un miglioramento prestazionale non corrispondesse un'impennata dei consumi.

Ryzen 5000 desktop, Zen 3 per la vittoria totale

A partire dalle CPU desktop (identificate dal nome in codice Vermeer), AMD non ha fatto mistero di essersi concentrata in modo particolare sull'IPC, ossia delle istruzioni calcolate ogni ciclo di clock. Nella transizione da Zen 2 e Zen 3 l'azienda ha fatto segnare un +19% (di media), superiore al balzo del 15% visto passando dai Ryzen 1000/2000 ai 3000. L'IPC rappresenta uno degli aspetti che definiscono la velocità dell'architettura, soprattutto in ambito single-thread o nei casi in cui sono usati pochi thread, come nei videogiochi.

Zen 3 nasce quindi per migliorare radicalmente uno dei punti più deficitari (ma non per questo insoddisfacenti) dei progetti Zen, Zen+ e Zen 2: Intel ha sempre avuto un vantaggio a tale riguardo, potendo inoltre sfruttare frequenze di clock molto spinte. Tutto questo, ovviamente, è stato fatto senza cedere lo scettro delle prestazioni in multi-threading. Il risultato netto l'abbiamo visto nei nostri articoli: i vari Ryzen 5000 sono ottimi sia per giocare sia per la produttività più spinta.

Zen 3 nasce quindi per migliorare radicalmente uno dei punti più deficitari (ma non per questo insoddisfacenti) dei progetti Zen, Zen+ e Zen 2: Intel ha sempre avuto un vantaggio a tale riguardo, potendo inoltre sfruttare frequenze di clock molto spinte. Tutto questo, ovviamente, è stato fatto senza cedere lo scettro delle prestazioni in multi-threading. Il risultato netto l'abbiamo visto nei nostri articoli: i vari Ryzen 5000 sono ottimi sia per giocare sia per la produttività più spinta.

Il progresso dell'IPC non è legato a un solo cambiamento. Zen 3, secondo AMD, è un'architettura realizzata da zero, anche se l'influenza dei progetti precedenti è palpabile e le novità interessano alcuni aspetti fondamentali: insomma, non c'è una vera e propria rivoluzione, ma un attento studio delle architetture precedenti per capire dove poter fare meglio senza pregiudicare quanto di buono offerto. Prima di addentrarci in alcuni aspetti più tecnici, è bene sapere che, in linea di continuità con i Ryzen 3000, anche i Ryzen 5000 hanno un progetto basato su chiplet, con uno o due Compute die affiancati da un I/O die sullo stesso package. La differenza chiara e lampante è che il progetto del chiplet è stato modificato con l'obiettivo di limitare gli accessi alla RAM, ridurre la latenza tra i core e quella tra i core e la cache. Tutto questo, secondo AMD, è utile nei giochi che in genere hanno un thread preferito che usa frequentemente la cache L3.

Nel caso della serie Ryzen 3000, i chiplet sono basati su un CCD (Core Complex Die) a 8 core composto da due CCX (CPU Complex o Core Complex) quad-core collegati dall'interconnessione Infinity Fabric. Le CPU con più di 8 core, e quindi dotate di due chiplet sul package, hanno perciò due CCD collegati da Infinity Fabric. Con l'architettura Zen 2, ogni CCX accede a 16 MB di cache L3 condivisa tra i quattro core, per un totale di 32 MB in ogni CCD. Per esempio, un Ryzen 9 3950X con 16 core è formato da 2 CCD e offre 64 MB di cache L3.

| Freq. base / boost | Cache L2/L3 | TDP | Dissipatore | PCIe | |

| Ryzen 9 5950X | 3.4 / 4.9 GHz | 8 MB L2 / 64 MB L3 | 105W | No | 24 linee PCIe 4.0 |

| Ryzen 9 5900X | 3.7 / 4.8 GHz | 6 MB L2 / 64 MB L3 | 105W | No | 24 linee PCIe 4.0 |

| Ryzen 7 5800X | 3.8 / 4.7 GHz | 4 MB L2 / 32 MB L3 | 105W | No | 24 linee PCIe 4.0 |

| Ryzen 5 5600X | 3.7 / 4.6 GHz | 3 MB L2 / 32 MB L3 | 65W | Wraith Stealth | 24 linee PCIe 4.0 |

Con i nuovi Ryzen 5000 Zen 3 la quantità di cache L3 non cambia ma non è più divisa in due: si tratta di un unico insieme da 32 MB accessibile dagli 8 core di un CCD. In un CCD c'è quindi un solo CCX. Ogni core accede al doppio della cache L3. Secondo AMD questa novità consente di far comunicare i core più rapidamente e porta a miglioramenti prestazionali in quei carichi che sfruttano appieno la cache L3. La cache L2 rimane pari a 512 KB per core e l'I/O die che affianca i chiplet è immutato rispetto alle CPU precedenti, anche dal punto di vista del processo produttivo (12 nm).

| Compute die | I/O die | |

| Matisse (Ryzen 3000, Zen 2) | 3,9 miliardi di transistor, 74 mm2 | 2,09 miliardi di transistor, 125 mm2 |

| Vermeer (Ryzen 5000, Zen 3) | 4,15 miliardi di transistor, 80 mm2 | 2,09 miliardi di transistor, 125 mm2 |

L'unica differenza dai Ryzen 3000 ai 5000 che interessa l'I/O die è che secondo AMD la frequenza "ideale" della memoria RAM per far rendere i Ryzen 5000 al meglio (anche se non è garantito) è 4000 MHz e non 3733 MHz. Questo cambiamento si deve alle tre frequenze al centro delle CPU Ryzen (oltre al clock dei core): la prima è la frequenza dell'interconnessione Infinity Fabric (fclk), che riguarda quanto rapidamente i core possono comunicare lungo il die della CPU e con i controller (PCIe, SATA, USB, ecc.). La seconda è la frequenza del controller di memoria (uclk), ed è la velocità con cui il controller può occuparsi dei comandi dalla RAM. La terza e ultima frequenza importante è quella della RAM stessa (mlck, memory clock).

Queste frequenze in rapporto 1:1:1 garantiscono le migliori prestazioni (se il rapporto cambia, sale la latenza) e secondo i suoi test interni, AMD ha rilevato che per i nuovi Ryzen 5000 il limite è 4000 MHz, non 3733 MHz come in precedenza. Nei nostri test abbiamo visto miglioramenti limitati in termini prestazionali passando da 3200 a 4000 MHz, quindi in genere acquistare una memoria tra quei due estremi permette alla CPU di esprimersi al meglio. I transfer rate supportati dalla nuova serie di CPU, a seconda della configurazione delle DIMM e dei rank, è la seguente:

| Configurazione DIMM | Rank | Transfer rate ufficialmente supportato (MT/s) |

| 2 di 2 | Single | DDR4-3200 |

| 2 di 4 | DDR4-3200 | |

| 4 di 4 | DDR4-2933 | |

| 2 di 2 | Dual | DDR4-3200 |

| 2 di 4 | DDR4-3200 | |

| 4 di 4 | DDR4-2667 |

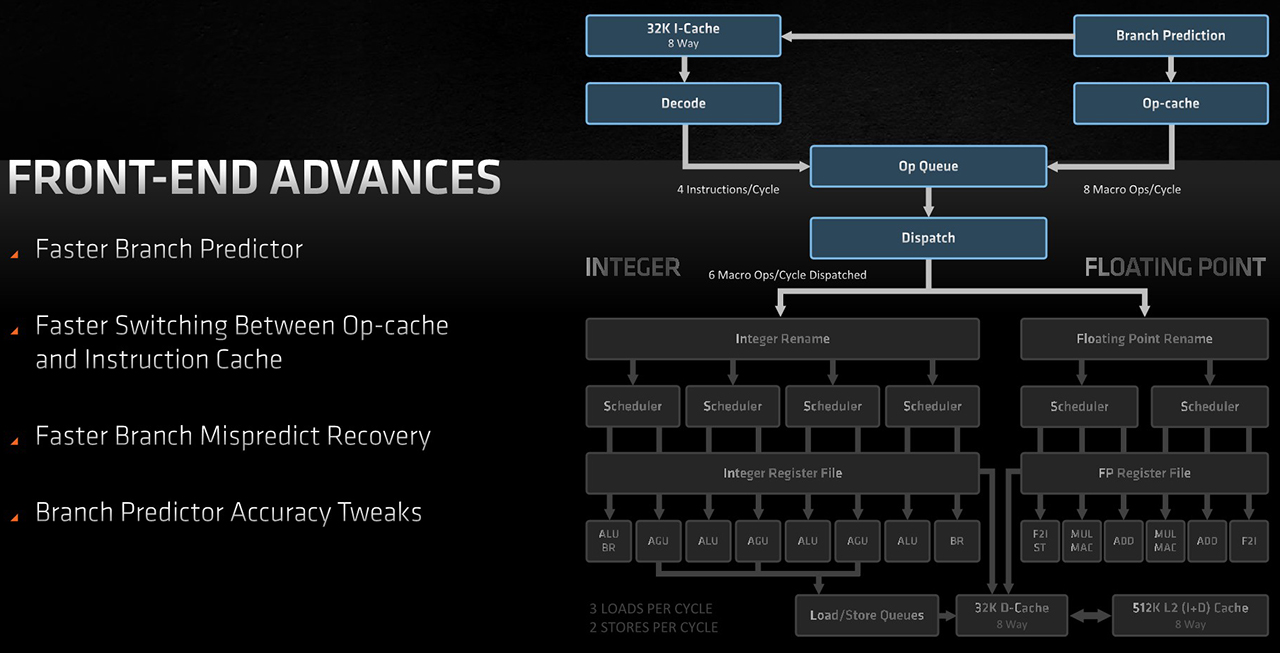

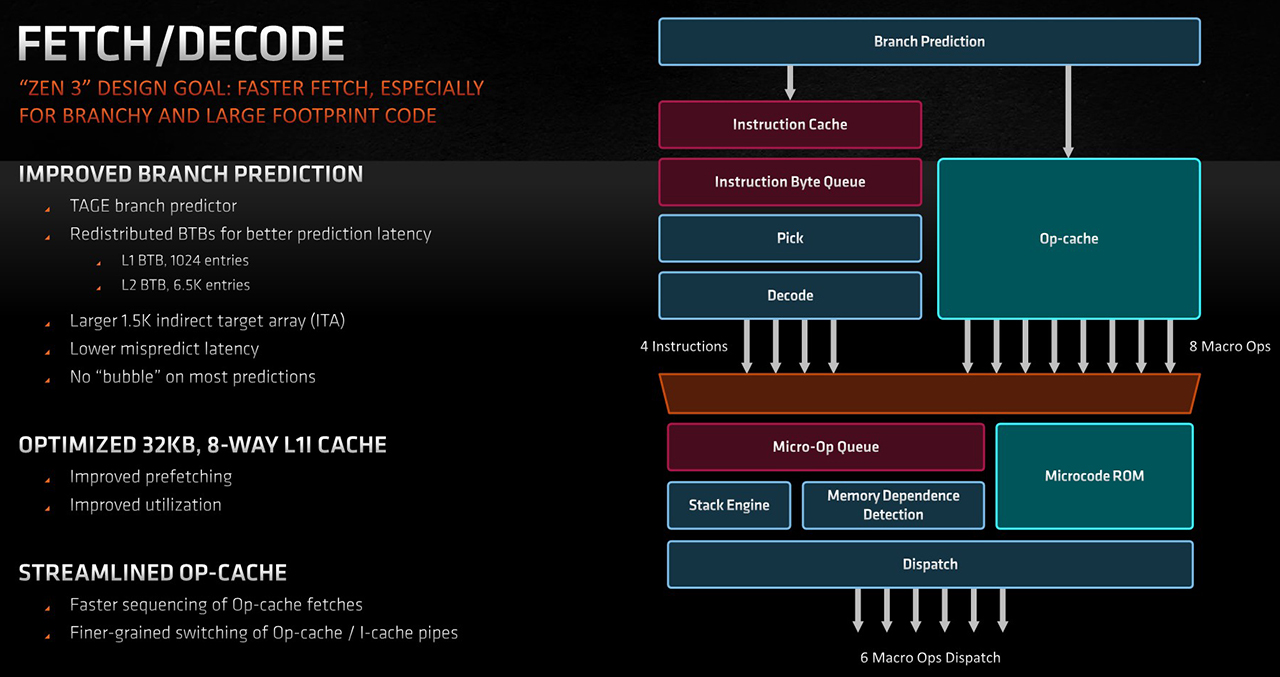

Dando uno sguardo all'architettura vera e propria, seppur a grandi linee, si osservano cambiamenti a partire dal front-end. AMD ha implementato un branch predictor più veloce (con una bandwidth maggiore) e accurato, capacità di ripresa migliori in caso di "predizioni" errate e un fetching (il recupero delle istruzioni dalla memoria) più veloce.

L'unità di branch prediction è un po' un "indovino": si occupa infatti di prevedere l'esito di un'operazione su cui si basa l'accettazione di una istruzione di salto condizionato. Ciò significa che il processore fa "un atto di fede" sulla direzione che prenderà una diramazione prima di conoscere il percorso corretto e la calcola in modo speculativo, anticipatamente. Se ci prende, la CPU non spreca cicli di clock e quindi svolge le operazioni con efficienza; se invece l'ipotesi si rivela errata, le istruzioni eseguite vengono scartate e si "rimbocca" il ramo (branch) corretto, il che porta a un ritardo e quindi a minori prestazioni.

Il front-end della CPU ha il compito di recuperare le istruzioni dalla memoria, decodificarle e metterle a disposizione delle unità di calcolo. Il suo compito è quindi quello di fornire un numero di µOP tale da tenere impegnato il back-end. Assicurarsi che quest'ultimo sia costantemente indaffarato è cruciale per permettere all'unità di calcolo di offrire le massime prestazioni.

Il miglioramento nella branch prediction si deve in parte a modifiche al TAGE (Tagged Geometry) Branch Predictor (più branch per ciclo). AMD ha raddoppiato la cache L1 del branch target buffer (BTB), con un passaggio da 512 a 1024 entry. Il BTB è una memoria di piccole dimensioni che serve per memorizzazione gli indirizzi di salto. Con entry ci si riferisce a una linea di memoria nella cache che contiene il dato copiato e un tag, ovvero la posizione di memoria richiesta. Quando il processore deve leggere o scrivere una posizione in memoria, controlla per prima cosa la "entry" corrispondente nella cache.

A fronte di un'espansione della BTB L1, AMD ha ridotto la cache BTB L2 a 6,5K entry per "preservare l'efficienza". L'azienda ha inoltre implementato una cache L1 istruzioni 8-way ottimizzata per un prefetching migliore. AMD ha lavorato anche sulle unità integer (calcolo numeri interi) e floating point (calcoli in virgola mobile), al fine di ridurre le latenze e alimentare i core più velocemente, senza perdere di vista l'efficienza energetica.

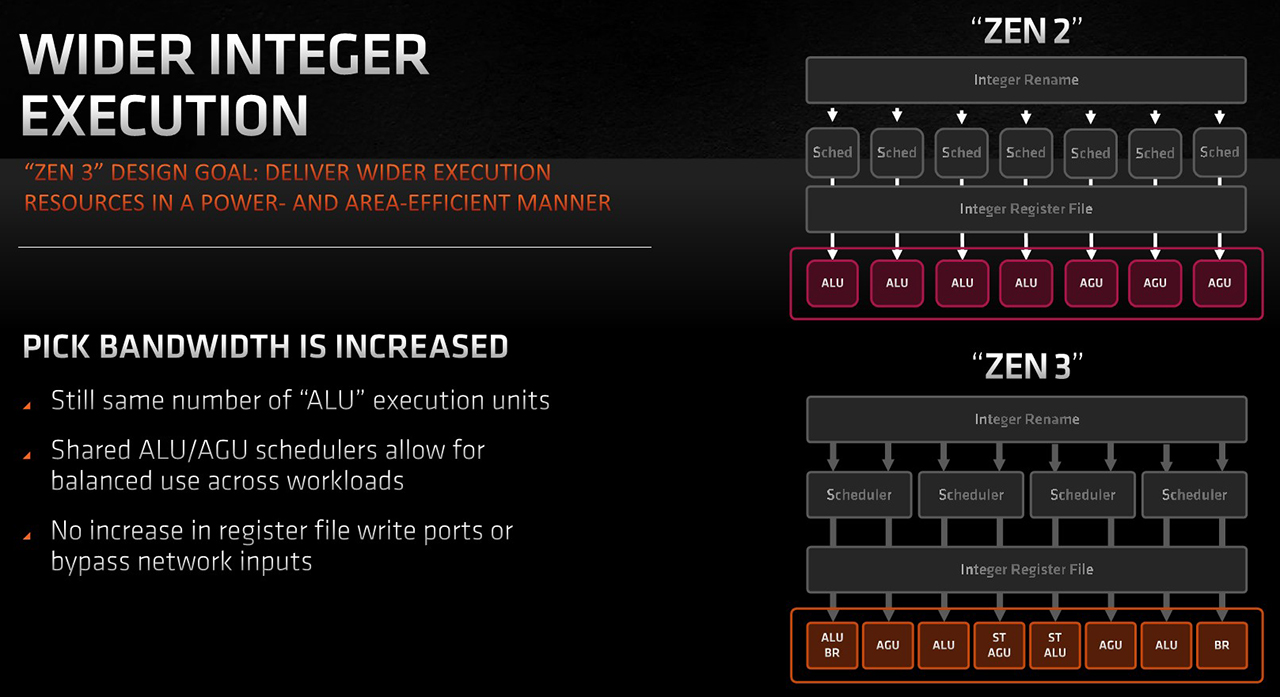

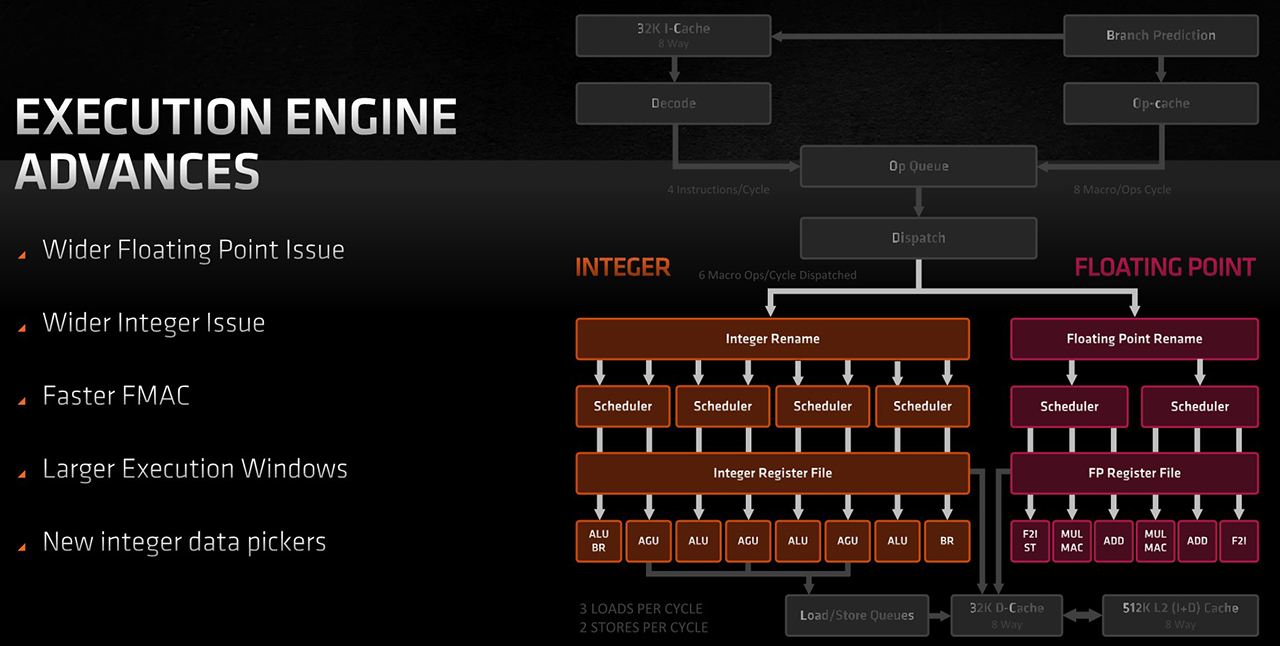

Entrambe le unità godono di un issue-width (il numero massimo di istruzioni avviabili durante lo stesso ciclo) maggiore, con finestre di esecuzione più ampie e unità di esecuzione con minore latenza. Il cambiamento principale per quanto concerne l'unità integer è il passaggio da otto scheduler per ogni unità di esecuzione a un progetto a quattro scheduler che indirizzano verso due unità di esecuzione ciascuno. Questi nuovi scheduler, oltre a essere più efficienti rispetto a quanto visto con Zen 2, vedono salire la loro capacità (entry) da 92 a 96.

AMD ha anche ampliato il file di registro fisico da 180 a 192 entry e il numero di issue dell'unità integer, che sale 7 a 10 nello stesso ciclo di clock. In modo simile a Zen 2 sono presenti 4 ALU (arithmetic logic unit, per i calcoli aritmetici), ma ci sono delle differenze in termini di configurazione: ci sono un totale di 10 unità che prevedono 3 AGU (address generation unit, per calcolare gli indirizzi che la CPU usa per accedere alla memoria principale), un branch dedicato e due per unità store. AMD cita anche un indirect target array (ITA) che sale a 1,5K rispetto alle 1024 entry di Zen 2 per la gestione di salti indiretti.

AMD afferma anche che non ci sono "bubble" (stalli nella pipeline) per quanto riguarda "la maggior parte delle predizioni". Una bubble è uno stadio della pipeline che non sta lavorando a causa di un ritardo nell'input. Questi stalli si propagano negli stadi successivi e si possono sommare: ridurre questi eventi è quindi fondamentale per l'efficienza dell'architettura. Tutto questo riduce le latenze interne al processore, espande la capacità delle diverse unità e aumenta il livello di parallelismo delle istruzioni.

Per quanto riguarda l'unità in virgola mobile, oltre ad aumentare la bandwidth di dispatch da 4 a 6 µOps, uno dei miglioramenti più importanti sul fronte della latenza è la riduzione di un ciclo - da 5 a 4 - nella gestione di operazioni fused multiply accumulate (FMAC).

I cambiamenti hanno l'effetto netto di portare a fare più calcoli per ciclo di clock. Per far sì che la memoria non rappresenti un collo di bottiglia, AMD ha migliorato la parte load/store di Zen 3 e aggiunto quattro TLB Walkers ai due esistenti, per un totale di sei. I TLB walker servono a gestire i "miss" del TLB (Translation Lookaside Buffer), ossia quando un indirizzo richiesto non è nel TLB. Quest'ultimo è una cache che serve a ridurre il tempo di accesso a una locazione di memoria utente. Il maggior numero di TLB Walkers consente di gestire un maggior numero di accessi concentrati alla memoria in determinati frangenti.

Oltre alle novità votate a migliorare le prestazioni dell'architettura, AMD si è curata anche di rafforzare le misure di sicurezza, un tema divenuto di grande importanza dopo i casi "Spectre e Meltdown". Rispetto a Zen 2, Zen 3 offre la Control-flow Enforcement Technology (CET), una misura integrata per la prima volta da Intel nei processori Tiger Lake. CET nasce per protegge i PC da comuni metodi di attacco malware che sono complessi da mitigare via software. CET impedisce l'uso scorretto di codice legittimo tramite attacchi di control-flow hijacking.

CET, nel caso delle CPU AMD Zen 3, offre agli sviluppatori una funzionalità chiamata shadow stack che protegge gli indirizzi di ritorno dai metodi di attacco basati su return-oriented programming (ROP). Return Oriented Programming (ROP) è una tecnica di attacco che sta guadagnando popolarità ed è particolarmente difficile da rilevare e prevenire perché i malintenzionati usano codice esistente attivo in memoria per modificare il comportamento di un programma.

Leggi anche: Processori AMD Ryzen: dalla serie 1000 a quella 5000, 38 CPU a confronto

Finora le soluzioni software per mitigare questi pericoli hanno restituito un successo limitato. I metodi di attacco includono tattiche come la corruzione dell'overflow del buffer dello stack e use-after-free. L'importanza di CET sta nel fatto che è parte integrante della microarchitettura ed è disponibile su tutta la famiglia di prodotti dotati di quel core.

Poiché annunciando CET Intel ha citato anche gli attacchi JOP (jump-oriented programming) e COP (call-oriented programming), abbiamo chiesto ulteriori delucidazioni AMD che ci ha assicurato che "i tre attacchi da voi citati (JOP, ROP, COP) possono essere mitigati in hardware o software. Tuttavia, solo ROP beneficia di mitigazioni a livello hardware, in quanto ciò preserva le prestazioni del processore e perciò è stato incluso in Zen 3. I prodotti AMD saranno inoltre protetti da attacchi JOP e COP tramite Microsoft Control Flow Guard (CFG) in Windows". L'architettura Zen 3 figura, inoltre, un'espansione dell'ISA (Instruction Set Architecture).

Ryzen 5000 mobile, Zen 3 ma non solo: oltre Cezanne spazio a Lucienne

Tutti i miglioramenti (prestazionali, di sicurezza e tecnici) di Zen 3 indicati per le CPU desktop valgono anche per le CPU mobile, anche se per essere precisi nel caso della Cezanne rispetto alle precedenti Renoir, si parla di un aumento delle prestazioni single-thread del 23% e un passo avanti in multi-thread del 17%. Rispetto al mondo desktop, dove i core Zen 3 sono integrati in chiplet affiancati da un I/O die, nelle nuove APU i core e tutto il resto delle funzionalità sono stipati all'interno di un unico chip. Sì, i chip per notebook sono dei cosiddetti processori "monolitici".

| Dimensioni e transistor | |

| Renoir (Ryzen 4000, Zen 2) | 156 mm2 - 9,8 miliardi di dollari |

| Cezanne (Ryzen 5000, Zen 3) | 180 mm2 - 10,7 miliardi di transistor |

Nel passaggio dai processori Ryzen 4000 basati su architettura Zen 2 ai 5000 Zen 3 ravvisiamo un raddoppio della cache L3, che peraltro diventa unificata: ora ci sono 8 core con accesso a 16 MB di cache L3, a fronte della configurazione precedente che vedeva due cluster da 4 core accedere a 4 MB di cache L3 ciascuno.

Le CPU Ryzen 5000 guadagnano inoltre il supporto alla memoria LPDDR4X, cosa che ne espande il raggio d'impiego, in quanto le LPDDR4 sono meno esigenti dal punto di vista energetico (e quindi sono usate specialmente nei notebook ad elevata autonomia). In termini prestazionali, il supporto alla LPDDR4X permette di supportare soluzioni fino a 4266 MT/s, teoricamente il 33% di bandwidth in più rispetto ai 3200 MT/s delle DDR4. Un altro vantaggio è che la LPDDR4X ha il doppio della densità della DDR4, quindi è possibile gestire fino a 32 GB in dual-channel.

| Modello | Architettura | Core / thread | Freq. Base | Freq. Boost | Cache | GPU | TDP |

|

Ryzen 5000 serie H |

|||||||

| Ryzen 9 5980HX | Zen 3 (Cezanne) | 8 / 16 | 3,3 GHz | 4,8 GHz | 20MB | 8 CU (2,1 GHz) | 45W+ |

| Ryzen 9 5980HS | Zen 3 (Cezanne) | 8 / 16 | 3 GHz | 4,8 GHz | 20MB | 8 CU (2,1 GHz) | 35W |

| Ryzen 9 5900HX | Zen 3 (Cezanne) | 8 / 16 | 3,3 GHz | 4,6 GHz | 20MB | 8 CU (2,1 GHz) | 45W+ |

| Ryzen 9 5900HS | Zen 3 (Cezanne) | 8 / 16 | 3 GHz | 4,6 GHz | 20MB | 8 CU (2,1 GHz) | 35W |

| Ryzen 7 5800H | Zen 3 (Cezanne) | 8 / 16 | 3,2 GHz | 4,4 GHz | 20MB | 8 CU (2 GHz) | 45W |

| Ryzen 7 5800HS | Zen 3 (Cezanne) | 8 / 16 | 2,8 GHz | 4,4 GHz | 20MB | 8 CU (2 GHz) | 35W |

| Ryzen 5 5600H | Zen 3 (Cezanne) | 6 / 12 | 3,3 GHz | 4,2 GHz | 19MB | 7 CU (1,8 GHz) | 45W |

| Ryzen 5 5600HS | Zen 3 (Cezanne) | 6 / 12 | 3 GHz | 4,2 GHz | 19MB | 7 CU (1,8 GHz) | 35W |

|

Ryzen 5000 serie U |

|||||||

| Ryzen 7 5800U | Zen 3 (Cezanne) | 8 / 16 | 1,9 GHz | 4,4 GHz | 20MB | 8 CU (2 GHz) | 15W |

| Ryzen 7 5700U | Zen 2 (Lucienne) | 8 / 16 | 1,8 GHz | 4,3 GHz | 12MB | 8 CU (1,9 GHz) | 15W |

| Ryzen 5 5600U | Zen 3 (Cezanne) | 6 / 12 | 2,3 GHz | 4,2 GHz | 19MB | 7 CU (1,8 GHz) | 15W |

| Ryzen 5 5500U | Zen 2 (Lucienne) | 6 / 12 | 2,1 GHz | 4 GHz | 11MB | 7 CU (1,8 GHz) | 15W |

| Ryzen 5 5400U | Zen 3 (Cezanne) | 4 / 8 | 2,6 GHz | 4 GHz | 10MB | 6 CU (1,6 GHz) | 15W |

| Ryzen 3 5300U | Zen 2 (Lucienne) | 4 / 8 | 2,6 GHz | 3,8 GHz | 6MB | 6 CU (1,6 GHz) | 15W |

AMD ci ha spiegato che il tape out delle CPU Zen 3 mobile è stato effettuato a pochi mesi da quello dell'introduzione commerciale delle CPU Zen 2 per notebook. Inoltre, i produttori di notebook hanno potuto riusare i progetti esistenti per un'integrazione più facile grazie al pinout identico. Non è un caso che AMD si aspetti 150 nuovi progetti quest'anno, 50 in più rispetto a quanto visto con i Ryzen 4000 lo scorso anno.

Le similarità delle CPU Zen 3 mobile e desktop sono tante e non possiamo certo stare a sindacare se le si accomuna, ma ci sono delle piccole differenze che probabilmente i più appassionati desiderano conoscere. In ambito mobile AMD ha lavorato sul controller di memoria introducendo uno stato di idle profondo in assenza di un carico sulla memoria, al fine di consumare meno energia, anche grazie alla possibilità di bypassare il PHY per ridurre le tensioni operative. AMD ha inoltre lavorato per far sì che il controller passi nello stato di uso massimo più rapidamente rispetto ai chip precedenti.

I processori Ryzen 5000 mobile Zen 3 godono inoltre di una migliore parte grafica, benché sia basata ancora su progetto Vega e non su una delle declinazioni di RDNA (1 o 2). La GPU può spingersi fino a 2,1 GHz, un boost di oltre 300 MHz rispetto ai modelli del 2020, garantendo al tempo stesso una tensione operativa più bassa. AMD è riuscita ad ampliare il budget energetico della grafica, portando così le prestazioni di calcolo potenziali a 2,14 TFLOPs con calcoli FP32 o 4,3 TFLOPS con quelli FP16 a precisione mista.

Applicando quanto appreso dai Ryzen 3000 desktop, AMD ha implementato nei modelli 5000 mobile quello che in gergo è definito Collaborative Power and Performance Control (CPPC). Cosa significa? Che le operazioni più leggere sono calcolate dai core più veloci, in modo da essere completate più velocemente al fine di un più rapido ritorno in stato di idle. Uno degli otto core è quindi etichettato come il migliore e tramite Windows tutti i carichi sfrutteranno quel core in modo preferenziale, se possibile.

Rispetto ai Ryzen 4000 mobile, i modelli 5000 hanno un controllo maggiore sulla regolazione della potenza. Laddove nella serie precedente la tensione operativa dei core e quella della GPU era la medesima senza differenze in base al carico, nel caso dei Ryzen 5000 abbiamo una gestione energetica più puntuale, e questo fa sì che ogni core funzioni alla sua tensione e frequenza ottimali. Ogni core è quindi capace di gestire la sua tensione operativa in modo indipendente. Si ottiene così una maggiore efficienza complessiva con carichi eterogenei che chiamano in causa le due anime della APU, con ulteriori possibilità di miglioramento legate all'ottimizzazione del sistema operativo nella distribuzione dei task.

Gestione energetica intelligente, ottimizzazioni all'interfaccia di memoria, regolazione della potenza per ogni core sul chip e il processo produttivo a 7 nanometri affinato, unitamente a miglioramenti in termini di piattaforma, hanno consentito ad AMD di ridurre il consumo energetico complessivo delle proprie APU a fronte di un incremento prestazionale.

L'architettura Zen 3 è alla base di tutte le APU della serie H di AMD (TDP da 35 e 45W+), otto modelli al momento (ricapitolati in tabella), mentre le proposte della serie U (da 15W) sono sei e non tutte sono Zen 3: tre sono basati su core Zen 2. AMD ha fatto un copia e incolla del progetto dei Ryzen 4000 modificando le frequenze? Non del tutto. Lucienne, questo il nome in codice dei Ryzen 5000 Zen 2 (i Ryzen 4000 si chiamano Renoir), non offre ovviamente la cache L3 unificata tipica di Zen 3, ma tutto il resto è presente. AMD ha inoltre lavorato per migliorare la tecnologia di clock gating, ossia quanto rapidamente un core può passare dallo stato idle alle prestazioni di picco e viceversa, riducendo ulteriormente quel tempo a 1-2 ms.

Un'altra differenza tra Renoir e Lucienne riguarda il controllo delle prestazioni da parte del sistema operativo o dal processore stesso. Con Renoir il sistema operativo controllava le prestazioni tramite i cosiddetti P-state, ovvero il sistema operativo richiedeva al processore un livello specifico di potenza e prestazioni in base al carico di lavoro rilevato e il processore rispondeva. Adesso, con Lucienne, il monitoraggio e il controllo della frequenza è svolto direttamente dal processore.

Infine, come i processori della serie H, anche nel caso di quelli della serie U c'è stato un lavoro sul firmware da parte di AMD per consentire alla GPU di regolare tensione e frequenza sulla base di una gestione energetica dinamica. Insieme a una migliore regolazione e un bilanciamento del budget di potenza tra CPU, interconnessione, DRAM e GPU, AMD è riuscita a dare alla GPU un tesoretto maggiore, e questo ha consenti al chip grafico integrato delle APU Lucienne di spingersi ancora più alto con la frequenza, salendo di un massimo di 150 MHz rispetto alle proposte integrate in Renoir.

L'architettura della maturità

Il percorso compiuto da AMD dal suo ritorno nel mondo delle CPU ad alte prestazioni consumer (2017) con una roadmap ben delineata è di quelli decisamente strabilianti. L'azienda, anno dopo anno, ha dimostrato di avere le idee chiare e soprattutto di saper rispettare le tempistiche: questo nel tempo ha rinnovato la fiducia degli appassionati e del mercato, a lungo incrinata, e ora nessuno la guarda più come il Calimero del mondo dei microprocessori.

Zen 3, migliorando sotto il profilo dell'IPC quel tanto che basta per ottenere lo scettro nel mondo del gaming, rappresenta l'architettura della maturità per l'azienda statunitense. Adesso all'appello manca solo il settore server con EPYC Milan, ma l'azienda promette grandi risultati anche in quell'ambito. Ora viene il bello: dove migliorare, come spingersi oltre, come non cedere il passo a una concorrenza che sicuramente vorrà rispondere al più presto? Staremo a vedere: lo sviluppo di Zen 4 e Zen 5 è già in corso da tempo e AMD sembra sicura delle sue carte.

Nel frattempo godiamoci i Ryzen 5000, processori che in ambito desktop sono "al vertice della catena alimentare" e nei notebook puntano a consolidare la ripresa vista in particolare nell'ultimo anno. A tal riguardo rimanete sintonizzati nelle prossime settimane, i notebook Ryzen 5000 stanno arrivando in redazione e non vediamo l'ora di metterli alla prova!

La rivoluzione dei dati in tempo reale è in arrivo. Un assaggio a Confluent Current 2025

La rivoluzione dei dati in tempo reale è in arrivo. Un assaggio a Confluent Current 2025 SAP Sapphire 2025: con Joule l'intelligenza artificiale guida app, dati e decisioni

SAP Sapphire 2025: con Joule l'intelligenza artificiale guida app, dati e decisioni Dalle radio a transistor ai Micro LED: il viaggio di Hisense da Qingdao al mondo intero

Dalle radio a transistor ai Micro LED: il viaggio di Hisense da Qingdao al mondo intero 'Napalm Girl': 400 fotografi contro la decisione del WPP di sospendere la paternità di Nick Ut

'Napalm Girl': 400 fotografi contro la decisione del WPP di sospendere la paternità di Nick Ut Gli italiani ce l'hanno più piccolo della media europea (il televisore)

Gli italiani ce l'hanno più piccolo della media europea (il televisore) Google Maps cambia logo nell'interfaccia mobile: ecco la piccola novità

Google Maps cambia logo nell'interfaccia mobile: ecco la piccola novità Windows 11 in calo a maggio, mentre cresce Windows 10 che a ottobre non sarà più supportato

Windows 11 in calo a maggio, mentre cresce Windows 10 che a ottobre non sarà più supportato Qual è lo smartphone più venduto in Europa? La TOP 10 è dominata due marchi

Qual è lo smartphone più venduto in Europa? La TOP 10 è dominata due marchi ECOVACS DEEBOT T50 PRO OMNI: il robot aspirapolvere da 15.000 Pa con lavaggio ad acqua calda è in offerta su Amazon a soli 699

ECOVACS DEEBOT T50 PRO OMNI: il robot aspirapolvere da 15.000 Pa con lavaggio ad acqua calda è in offerta su Amazon a soli 699 Apple Watch: tutte le offerte su Amazon a Giugno! Series 10 da 46mm a soli 359, sconti anche su Series 9 e SE

Apple Watch: tutte le offerte su Amazon a Giugno! Series 10 da 46mm a soli 359, sconti anche su Series 9 e SE La Via Lattea e la galassia di Andromeda potrebbero non scontrarsi secondo nuovi dati di Hubble e Gaia

La Via Lattea e la galassia di Andromeda potrebbero non scontrarsi secondo nuovi dati di Hubble e Gaia Samsung, finisce l'idillio con Google? Su Galaxy S26 potrebbe arrivare Perplexity al posto di Gemini

Samsung, finisce l'idillio con Google? Su Galaxy S26 potrebbe arrivare Perplexity al posto di Gemini Squid Game 3, il trailer della terza stagione è qui! Trama, cast e data di uscita

Squid Game 3, il trailer della terza stagione è qui! Trama, cast e data di uscita Speciale offerte videocamere e webcam Insta360: 6 modelli tra 4K, 8K, POV e panoramiche a 360°

Speciale offerte videocamere e webcam Insta360: 6 modelli tra 4K, 8K, POV e panoramiche a 360° Microsoft annuncia diverse novità su Windows in Europa, per una maggiore adesione al DMA

Microsoft annuncia diverse novità su Windows in Europa, per una maggiore adesione al DMA Stranger Things 5: ecco il trailer e la data di uscita della stagione finale su Netflix

Stranger Things 5: ecco il trailer e la data di uscita della stagione finale su Netflix Sconti PlayStation 5 su Amazon: Slim con 2 DualSense a 459, PS VR2 a 399 e PS5 Pro in offerta a 749

Sconti PlayStation 5 su Amazon: Slim con 2 DualSense a 459, PS VR2 a 399 e PS5 Pro in offerta a 749

33 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoPersonalmente penso si a tanto roba, purtoppo sono ancora fossilizzato su Intel ed avrei una gran curiosità di provarli... C'èancatonpoco per prendere un 4600h con l' Honor book pro 16 pollici...

Sara per la prossima con un 5600h...

L'unico appunto che mi sento di fare (anche perché poi è l'unica cosa su cui mi sento un peletto più ferrato rispetto agli altri argomenti trattati) è su CET.

in realtà i due elementi (CET, Spectre) sono slegati (tant'è vero che le prime enunciazioni di CET sono antecedenti quantomeno di un paio d'anni).

Microsoft, in sostanza, ha constatato l'impossibilità di contrastare completamente in_software gli attacchi che prevedono il riutilizzo di porzioni di codice presente in memoria per fini diversi da quelli per cui erano stati originariamente pensati (è una sorta di abuso di elementi di per se innocui che, una volta opportunamente concatenati, generano un risultato inatteso ma evidentemente controllato dall'attaccante), da qui allora la richiesta d'aiuto ai produttori di CPU (il tentativo infatti di 'risolverla in_software' era fallito, vedi anche quello che è stato di Return Flow Guard).

Link ad immagine (click per visualizzarla)

Poi è venuto Spectre (2018?)..

Grazie!

Ciao, non volevo mettere tutto insieme o far passare che CET fosse susseguente a Meltdown e Spectre, se è così forse mi sono espresso male ma poco importa. Volevo semplicemente dire che CET arriva in un periodo storico dove l'aspetto della sicurezza in hardware ha assunto molto più peso che in passato. Grazie cmq dell'appunto!

GRAZIE!

Si beh non sono una valanga ma alla fine si trovano abbastanza facilmente a prezzi diciamo più o meno in linea con quelli proposti dalla casa.

il delirio di follia sono le GPU.

..e la cosa non accenna minimamente a calmarsi.

Anche se da parte mia, non essendo un'esperto dell'argomento, la comprensione di alcuni dettagli e termini non è così automatica.

In ogni caso complimenti all'autore perché mi ha reso le idee più chiare.

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".