TSMC non ha paura di Intel: il nostro processo N3P al livello di 18A, ma più maturo e meno costoso

C.C. Wei, amministratore delegato di TSMC, ha parlato della sfida con Intel nel campo dei processi produttivi: la società taiwanese pensa di avere in mano una soluzione migliore di Intel 18A già con il processo N3P. Il passaggio a N2 sancirà un chiaro vantaggio.

di Manolo De Agostini pubblicata il 20 Ottobre 2023, alle 09:01 nel canale ProcessoriTSMCIntel

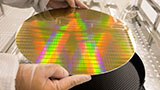

La taiwanese TSMC ritiene che il suo processo produttivo N3P sia competitivo, se non superiore, con Intel 18A, tecnologia che il produttore dei microprocessori Core intende applicare alla produzione di chip tra la fine del 2024 e il 2025.

"La nostra valutazione interna mostra che il nostro N3P […] si è dimostrato paragonabile [in termini di prestazioni energetiche] a [Intel] 18A, la tecnologia del nostro concorrente, ma con un time to market anticipato, una migliore maturità tecnologica e costi molto migliori", ha affermato C.C. Wei, amministratore delegato di TSMC a margine di una conference call. "In effetti, lasciatemi ripetere ancora una volta, la nostra tecnologia a 2 nm senza alimentazione dal retro (N2) è più avanzata sia di N3P che di 18A e, quando verrà introdotta nel 2025, sarà la tecnologia più avanzata del settore dei semiconduttori".

TSMC produce già "a 3 nanometri", ma quando si parla di processi N3 non si parla di una singola soluzione bensì di una famiglia - ne abbiamo scritto lo scorso aprile. N3P è un processo per cui si prevede la produzione in volumi nella seconda metà del 2024 e si tratta di un'evoluzione di N3E con transistor ottimizzati che consentono di aumentare le prestazioni del 5% con la stessa dispersione o ridurre il consumo del 5% ~ 10% alla stessa frequenza.

Il nuovo processo incrementa anche la densità dei transistor del 4% per quei progetti che TSMC definisce "misti", cioè quelli costituiti da circuiti logici al 50%, SRAM al 30% e componenti analogici al 20%. La fonderia taiwanese ha migliorato la densità di N3P intervenendo sulle prestazioni ottiche dei suoi scanner. N3P mantiene le regole di progettazione di N3E, consentendo ai progettisti di portare i design sviluppati su N3E al nuovo processo.

Intel 18A, invece, punta a garantire un miglioramento delle prestazioni per watt rispetto a Intel 20A del 10% circa. I punti forti di questo processo - così come di quello 20A - sono PowerVia, un'innovativa tecnologia di alimentazione per i chip dal retro, insieme ai transistor Gate All Around (GAA) ribattezzati RibbonFET.

Il leader di TSMC sembra convinto di poter mettere il bastone tra le ruote alle aspirazioni di Pat Gelsinger, il quale punta a riportare Intel al vertice nel 2025 dal punto di vista tecnologico, prestazionale e produttivo.

La famiglia di processi N3 di TSMC continua a essere basata su transistor FinFET e la tradizionale tecnologia di alimentazione. Il passaggio a soluzioni analoghe a RibbonFET e PowerVIA avverrà con calma, nel primo caso con il processo N2 dal 2025 inoltrato, nel secondo con N2P nel corso del 2026.

Non sappiamo se le parole di TSMC siano volte a tranquillizzare mercato e clienti o semplicemente pura e semplice verità. Nel caso lo fossero, rappresenterebbero una bella stoccata alle ambizioni di Intel e alla sua roadmap aggressiva di introdurre 5 processi in 4 anni: roadmap che, confronti a parte, Intel deve rispettare se vuole non solo competere meglio con i suoi prodotti ma anche attrarre clienti per le sue Fab.

BOOX Note Air4 C è uno spettacolo: il tablet E Ink con Android per lettura e scrittura

BOOX Note Air4 C è uno spettacolo: il tablet E Ink con Android per lettura e scrittura Recensione Sony Xperia 1 VII: lo smartphone per gli appassionati di fotografia

Recensione Sony Xperia 1 VII: lo smartphone per gli appassionati di fotografia Attenti a Poco F7: può essere il best buy del 2025. Recensione

Attenti a Poco F7: può essere il best buy del 2025. Recensione DJI OSMO Mobile SE a 69: il gimbal compatto che trasforma i video dello smartphone in riprese da pro

DJI OSMO Mobile SE a 69: il gimbal compatto che trasforma i video dello smartphone in riprese da pro Scope elettriche da record su Amazon: due modelli potentissimi sotto i 120, ecco perché piacciono così tanto

Scope elettriche da record su Amazon: due modelli potentissimi sotto i 120, ecco perché piacciono così tanto GTA 6 a 80 euro? Take-Two frena sul prezzo e punta tutto sul valore percepito

GTA 6 a 80 euro? Take-Two frena sul prezzo e punta tutto sul valore percepito I 3 portatili più convenienti su Amazon: sono 2 tuttofare Lenovo e un HP Victus gaming con RTX 5060

I 3 portatili più convenienti su Amazon: sono 2 tuttofare Lenovo e un HP Victus gaming con RTX 5060 AirPods Pro 2 a soli 199: su Amazon anche AirPods 4 in sconto, ecco le differenze che contano

AirPods Pro 2 a soli 199: su Amazon anche AirPods 4 in sconto, ecco le differenze che contano 2 Smart TV 4K Hisense con doppio sconto su Amazon: sono OLED e QLED, 55" e 75", fateci un bel pensierino

2 Smart TV 4K Hisense con doppio sconto su Amazon: sono OLED e QLED, 55" e 75", fateci un bel pensierino Portatili Apple ai minimi: MacBook Pro con chip M4 a 1.648 e Macbook Air 13 16GB7256GB, sempre M4, a 998

Portatili Apple ai minimi: MacBook Pro con chip M4 a 1.648 e Macbook Air 13 16GB7256GB, sempre M4, a 998 Come mantenere Windows 10 sicuro dopo il 2025: tutto sul programma ESU

Come mantenere Windows 10 sicuro dopo il 2025: tutto sul programma ESU Finalmente è tornato su Amazon l'iPhone 16 128GB a 749, in tutti i colori, ma ci sono anche i 16e e 16 Pro in offerta

Finalmente è tornato su Amazon l'iPhone 16 128GB a 749, in tutti i colori, ma ci sono anche i 16e e 16 Pro in offerta Auto nuove? Per il 65% degli italiani sono troppo care, non dovrebbero costare oltre i 20.000 euro

Auto nuove? Per il 65% degli italiani sono troppo care, non dovrebbero costare oltre i 20.000 euro Droni solari Airbus volano nella stratosfera grazie alle nuove batterie al silicio: test riusciti a oltre 20 km di quota

Droni solari Airbus volano nella stratosfera grazie alle nuove batterie al silicio: test riusciti a oltre 20 km di quota Colpo da 15 milioni di dollari: chi ha rubato un carico di prodotti AMD e Apple?

Colpo da 15 milioni di dollari: chi ha rubato un carico di prodotti AMD e Apple? Elon Musk lancia l'allarme su GPT-5: 'OpenAI divorerà Microsoft'. Ma Nadella lo sfida con un sorriso

Elon Musk lancia l'allarme su GPT-5: 'OpenAI divorerà Microsoft'. Ma Nadella lo sfida con un sorriso iPhone 17 Pro sarà più costoso, ma anche più conveniente

iPhone 17 Pro sarà più costoso, ma anche più conveniente

7 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoI ricercatori cinesi stessi dicevano che la strada è ancora lunga, non aspetterei questa tecnologia col fiato sospeso

Se ci basiamo già oggi sulle nostre esperienze di mercato già ora i margini di guadagno prestazionale a cui abbiamo assistito passando dal vecchio 7nm o ancora peggio dal 8nm di Samsung delle scorse generazioni a questi ultimi 5/4nm di TSMC c'è stato un gap al di sotto delle aspettative per me.

Una volta il processo produttivo era nominato in base alla feature size dei CMOS "planari" ed erano prodotti proiettando luce (prima visibile, ora ultravioletta) su maschere fotolitografiche simili ai negativi delle macchine fotografiche a pellicola.

Adesso non é più così da molti anni.

Al posto di "negativi" si usano più reticoli di diffrazione per ottenere un risultato simile a quel che si otteneva con un singolo "negativo".

Questo perché la lunghezza d'onda usata per la fotolitografia EUV é 13.5 nm ed usata con semplici "negativi" non permette di scendere ai livelli "nominali" attuali.

Con la fotolitografia DUV é anche peggio, lunghezza d'onda 193 nm, che usando tecniche ad immersione permette di scendere a circa 50nm.

Per questo, specialmente da quando si usano FinFET e GAA/RibbonFET i "nanometri" di un processo produttivo sono una stima di quale dovrebbe essere la feature size di un processo fotolitografico "planare" con "negativi" ed una fonte di "luce" con lunghezza d'onda molto più piccola di quella effettivamente utilizzata.

I processi utilizzati da Intel, TSMC, Samsung ecc. non sono più comparabili, visto che molto dipende da quanti passaggidi produzione venfoni fatti, cone vengobo fatti, a quali livelli il software di progettazione simula correttamente il prodotto reale (e parlo di singoli gate), ecc. ecc.

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".