Google Trillium: la TPU di sesta generazione è cinque volte più veloce e molto più efficiente

Google continua a sviluppare l'hardware che le serve per mettere a punto e gestire modelli di intelligenza artificiale sempre più avanzati. Nel corso della Google I/O si è parlato di Trillium, la Tensor Processing Unit di sesta generazione, più potente ed efficiente.

di Manolo De Agostini pubblicata il 16 Maggio 2024, alle 07:41 nel canale ProcessoriGoogle, durante l'evento annuale Google I/O, ha svelato la sesta generazione della sua TPU (Tensor Processing Unit), la soluzione hardware progettata in casa con l'obiettivo di accelerare carichi di intelligenza artificiale.

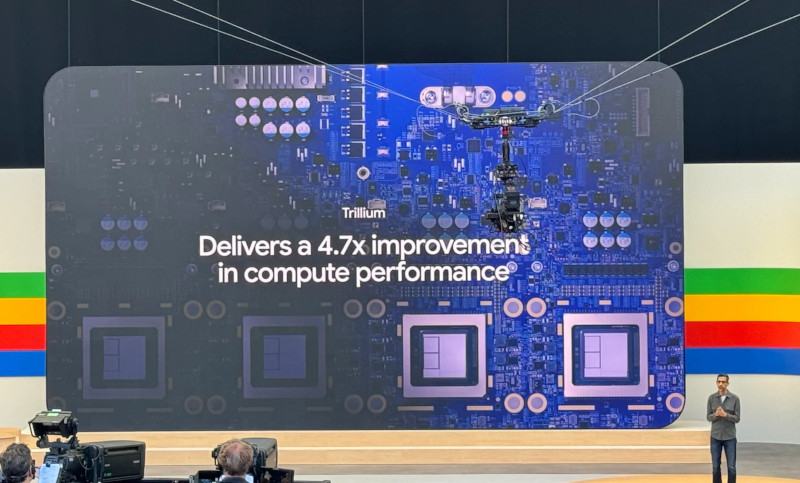

La nuova arrivata, nome in codice Trillium, è stata definita come "la TPU più performante ed energeticamente efficiente" che finora Google abbia mai realizzato. Una frase scontata, ma contestualizzata dai primi numeri diffusi.

"Le TPU Trillium raggiungono un impressionante aumento di 4,7 volte delle prestazioni di calcolo di picco per chip rispetto alla TPU v5e", spiega la casa di Mountain View.

"Abbiamo raddoppiato la capacità e la larghezza di banda della memoria HBM e anche la larghezza di banda dell'interconnessione tra chip (ICI, Interchip Interconnect) rispetto alla TPU v5e. Inoltre, Trillium è dotato di SparseCore di terza generazione, un acceleratore specializzato nell'elaborazione di embedding di dimensioni ultra-grandi, comuni nei carichi di lavoro avanzati di classificazione e raccomandazione".

Secondo Google, le TPU Trillium consentono di addestrare più rapidamente la nuova ondata di modelli e servirli con una latenza ridotta e a costi inferiori. Le TPU Trillium, inoltre, sono più efficienti dal punto di vista energetico di oltre il 67% rispetto alle TPU v5e.

Osservando la scheda tecnica della TPU v5e, le dichiarazioni di Google suggeriscono che il nuovo chip sia in grado di raggiungere circa 926 teraFLOPS nel formato BF16 e 1847 teraFLOPS con dati in formato INT8. Ciò presuppone che Google non si affidi a formati INT4 o FP4 a bassa precisione per raggiungere quel risultato, come fa NVIDIA con i chip Blackwell.

Oltre agli SparseCore, Google ha incrementato le dimensioni delle matrix multiple unit (MXU) del chip e alzato la frequenza di clock. Si stima che la memoria HBM a bordo di Trillium sia pari a 32 GB, capace di una bandwidth di 1,6 TB/s, mentre l'interconnessione chip-to-chip dovrebbe toccare i 3,2 Tbps.

In termini di scalabilità, Trillium sembra abbastanza simile alle istanze v5e che sostituisce in quanto supporta Pod con un massimo di 256 chip. Più Pod possono essere collegati in rete, arrivando a mettere in comunicazione "decine di migliaia di chip".

Recensione Sony Xperia 1 VII: lo smartphone per gli appassionati di fotografia

Recensione Sony Xperia 1 VII: lo smartphone per gli appassionati di fotografia Attenti a Poco F7: può essere il best buy del 2025. Recensione

Attenti a Poco F7: può essere il best buy del 2025. Recensione Recensione Samsung Galaxy Z Fold7: un grande salto generazionale

Recensione Samsung Galaxy Z Fold7: un grande salto generazionale  L'amministrazione Trump vorrebbe distruggere un satellite per la rilevazione delle emissioni di anidride carbonica e non solo

L'amministrazione Trump vorrebbe distruggere un satellite per la rilevazione delle emissioni di anidride carbonica e non solo La NASA vorrebbe realizzare un reattore nucleare sulla Luna per le future missioni con equipaggio

La NASA vorrebbe realizzare un reattore nucleare sulla Luna per le future missioni con equipaggio Oltre 1.700 km con una ricarica: l'assurdo record di autonomia del Chevrolet Silverado

Oltre 1.700 km con una ricarica: l'assurdo record di autonomia del Chevrolet Silverado Maxi annuncio dalla Casa Bianca: Apple potrebbe investire 100 miliardi di dollari aggiuntivi negli USA

Maxi annuncio dalla Casa Bianca: Apple potrebbe investire 100 miliardi di dollari aggiuntivi negli USA Microonde con grill, super venduto e apprezzato, a 55? Senza dubbio il modello Cecotec, pratico e senza fronzoli inutili

Microonde con grill, super venduto e apprezzato, a 55? Senza dubbio il modello Cecotec, pratico e senza fronzoli inutili Pubblicazioni scientifiche false in aumento vertiginoso: il fenomeno dei paper mill minaccia la credibilità accademica

Pubblicazioni scientifiche false in aumento vertiginoso: il fenomeno dei paper mill minaccia la credibilità accademica Ecco le 100 startup che prenderanno parte a DigithON 2025

Ecco le 100 startup che prenderanno parte a DigithON 2025 Pandora colpita da un attacco informatico: rubati nomi ed email, ma non password e carte di credito

Pandora colpita da un attacco informatico: rubati nomi ed email, ma non password e carte di credito Cooler Master MasterFrame 360 Panorama S Limited Edition: solo 100 pezzi al mondo

Cooler Master MasterFrame 360 Panorama S Limited Edition: solo 100 pezzi al mondo Motorola e Swarovski lanciano The Brilliant Collection con cristalli Swarovski

Motorola e Swarovski lanciano The Brilliant Collection con cristalli Swarovski Wikipedia dichiara guerra all'IA spregiudicata: cancellazione rapida per gli articoli non revisionati

Wikipedia dichiara guerra all'IA spregiudicata: cancellazione rapida per gli articoli non revisionati Dai social ai farmaci dimagranti: il nuovo incarico della ex CEO di X (Twitter)

Dai social ai farmaci dimagranti: il nuovo incarico della ex CEO di X (Twitter) Addio spam su WhatsApp? Ecco le nuove difese contro l'aggiunta indesiderata nei gruppi

Addio spam su WhatsApp? Ecco le nuove difese contro l'aggiunta indesiderata nei gruppi Su Windows 11 25H2 cambierà (in peggio?) la gestione dei collegamenti sul desktop

Su Windows 11 25H2 cambierà (in peggio?) la gestione dei collegamenti sul desktop

1 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoDevi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".