Intel Sandy Bridge: analisi dell'architettura

Dopo aver valutato le capacità prestazionali delle prime CPU Intel della famiglia Sandy Bridge passiamo ad un'analisi dell'architettura, frutto di una profonda evoluzione di quanto di valido Intel ha implementato in Nehalem.

di Paolo Corsini pubblicato il 07 Gennaio 2011 nel canale ProcessoriIntel

Last Level Cache, Ring bus e System Agent

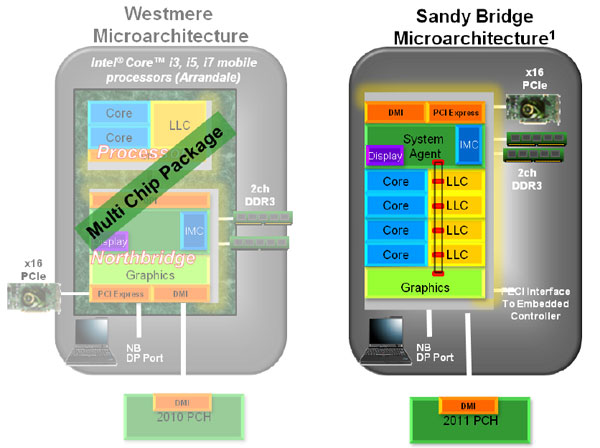

Abbiamo già evidenziato come uno degli elementi peculiari delle soluzioni Sandy Bridge sia rappresentato dalla piena integrazione tra CPU e GPU all'interno dello stesso componente di silicio. Analizzando più in dettaglio l'architettura di questi processori scopriamo tuttavia come l'integrazione sia stata spinta ad un livello ancor più elevato in Sandy Bridge rispetto a quanto fatto sino ad ora da Intel.

In Sandy Bridge troviamo CPU e GPU che condividono la cache di terzo livello, indicata da Intel come Last Level Cache o LLC. Memory controller e controller PCI Express sono nuovamente integrati all'interno della CPU. Troviamo anche un nuovo componente, indicato con il nome di System Agent, che di fatto implementa tutte le funzionalità che in passato sono state riservate al north bridge del chipset.

Particolarmente interessante è l'implementazione sviluppata da Intel per la Last Level Cache, che vede un design di tipo Ring composto da 4 anelli: 32 byte Data ring, Request ting, Arknowledge ring e Snoop ring. Si tratta dello stesso ring sviluppato da Intel per le soluzioni Nehalem EX e Westmere EX, le soluzioni per la famiglia Xeon di fascia più alta disponibili sul mercato.

Il ring è di tipo fully pipelined, pertanto opera alle stesse frequenze di clock e tensione della componente core. Il ring non è bidirezionale, ma i punti di stop presenti all'altezza dei core, della GPU e del System Agent permettono di fatto di andare in direzione up e down. Il ring bus gestisce coherency, ordering e core interface per bilanciare al meglio la distribuzione delle richieste all'interno del ring; non c'è più un arbitrer centralizzato come in Nehalem, cosa che migliora sensibilmente la scalabilità soprattutto al crescere del numero dei core

Gli accessi al ring sono configurati in modo tale da seguire sempre il path più corto, minimizzando la latenza complessiva. Intel dichiara una latenza della cache LLC variabile da da 26 a 31 cicli di clock, inferiore ai 36 cicli di clock di media delle soluzioni Nehalem.

La bandwidh che un ring configurato in questo modo mette a disposizione è estremamente elevata: per ogni core abbiamo infatti 96 Gbytes al secondo, per un totale di 384 Gbytes al secondo di picco prendendo quale riferimento un processore Sandy Bridge con architettura quad core.

La cache è divisa in porzioni in funzione del numero di core presenti; ogni core, tuttavia, può accedere in modo completamente indipendente a qualsiasi componente della LLC. Ogni agent può accedere a tutti i dati presenti nella LLC, indipendentemente da chi abbia allocato la specifica line, dopo che è stato eseguito il check dei memory range. La quantità di cache LLC alla quale può accedere la GPU può essere limitata; questo non avviene invece mai per la CPU. Il limite da lato GPU è funzione del tipo di SKU, dal quantitativo di LLC disponibile e dal tipo di sottosistema video che è stato integrato nel processore.

In Sandy Bride Intel ha implementato 3 differenti power domains: il primo, fisso, è per il System Agent, il secondo per i Cores e il Ring di tipo variabile e l'ultimo dedicato alla componente video, anche in questo caso di tipo variabile.

Chiudiamo con il System Agent, nome che di fatto identifica quella che nelle architetture Nehalem era noto come componente Uncore. Questo elemento contiene al proprio interno power control unit, DMI, memory controller DDR3 dual channel, controller PCI Express a 16 linee elettriche e display engine per gestire il segnale video. Il ring stop del system agent non ha bandwidth massima sino a 96 Gbytes al secondo come gli altri, in quanto è limitato dalla bandwidth del controller PCI Express e del memory controller DDR3.

La rivoluzione dei dati in tempo reale è in arrivo. Un assaggio a Confluent Current 2025

La rivoluzione dei dati in tempo reale è in arrivo. Un assaggio a Confluent Current 2025 SAP Sapphire 2025: con Joule l'intelligenza artificiale guida app, dati e decisioni

SAP Sapphire 2025: con Joule l'intelligenza artificiale guida app, dati e decisioni Dalle radio a transistor ai Micro LED: il viaggio di Hisense da Qingdao al mondo intero

Dalle radio a transistor ai Micro LED: il viaggio di Hisense da Qingdao al mondo intero Una domenica bestiale Amazon: LG OLED, super portatile Lenovo, iPhone 16 Pro e Pro Max, robot e altri super sconti

Una domenica bestiale Amazon: LG OLED, super portatile Lenovo, iPhone 16 Pro e Pro Max, robot e altri super sconti DJI Mini 4 Pro Fly More Combo: drone leggero che non richiede il patentino oggi in offerta super su Amazon

DJI Mini 4 Pro Fly More Combo: drone leggero che non richiede il patentino oggi in offerta super su Amazon realme GT 7T: display da 6000 nit, potentissimo, 7000 mAh, quasi un top di gamma a metà del prezzo che ti aspetti

realme GT 7T: display da 6000 nit, potentissimo, 7000 mAh, quasi un top di gamma a metà del prezzo che ti aspetti Ancora qualche pezzo per il portatile Lenovo con Core i7, 40GB RAM e 1TB SSD: va sempre a ruba

Ancora qualche pezzo per il portatile Lenovo con Core i7, 40GB RAM e 1TB SSD: va sempre a ruba TV OLED LG Serie C4 2024: immagini da cinema e 4K a 144Hz in sconto su Amazon

TV OLED LG Serie C4 2024: immagini da cinema e 4K a 144Hz in sconto su Amazon Smartwatch Amazfit in sconto: Active 2 a 97, ma ci sono offerte su tutta la gamma

Smartwatch Amazfit in sconto: Active 2 a 97, ma ci sono offerte su tutta la gamma Router e ripetitori AVM FRITZ! da 30 su Amazon: ecco tutte le offerte da non perdere

Router e ripetitori AVM FRITZ! da 30 su Amazon: ecco tutte le offerte da non perdere Adulting 101: i corsi per imparare come era la vita fino a qualche anno fa

Adulting 101: i corsi per imparare come era la vita fino a qualche anno fa Blue Origin ha lanciato con successo la missione suborbitale NS-32 con New Shepard

Blue Origin ha lanciato con successo la missione suborbitale NS-32 con New Shepard L'amministrazione Trump ha ritirato la candidatura di Jared Isaacman come amministratore della NASA

L'amministrazione Trump ha ritirato la candidatura di Jared Isaacman come amministratore della NASA La NASA potrebbe chiudere le missioni OSIRIS-APEX, New Horizons e Juno cancellandone altre per risparmiare soldi

La NASA potrebbe chiudere le missioni OSIRIS-APEX, New Horizons e Juno cancellandone altre per risparmiare soldi Trump vieta anche la vendita di software per la progettazione di chip alle società cinesi

Trump vieta anche la vendita di software per la progettazione di chip alle società cinesi Le migliori offerte del weekend Amazon: portatili, robot, iPhone, Kindle ai prezzi più bassi di sempre

Le migliori offerte del weekend Amazon: portatili, robot, iPhone, Kindle ai prezzi più bassi di sempre Dreame L40 Ultra a 699, prezzo shock: vale quasi quanto lX40 Ultra da 999 (ma costa 300 in meno!)

Dreame L40 Ultra a 699, prezzo shock: vale quasi quanto lX40 Ultra da 999 (ma costa 300 in meno!)