AMD fornisce nuovi dettagli sull'architettura delle CPU Zen

Si avvicina il debutto della prossima generazione di processori AMD, appartenenti alla famiglia Zen: l'azienda americana fornisce nuovi dettagli sull'architettura alla conferenza Hot Chips, ma per le versioni e le frequenze c'č da attendere ancora

di Paolo Corsini pubblicata il 24 Agosto 2016, alle 15:31 nel canale ProcessoriAMDZen

In occasione della conferenza Hot Chips, che si sta svolgendo in questi giorni a Stanford, AMD ha fornito ulteriori informazioni sull'architettura alla base dei propri processori della famiglia Zen. Con questo nome vengono indicate le CPU di prossima generazione, attese al debutto commerciale all'inizio del 2017 ferma restando la possibilità che alcune di questi processori vengano venduti in un primo lotto già entro la fine del 2016.

La scorsa settimana l'azienda americana ha effettuato una dimostrazine pubblica di questi processori mostrando un sistema desktop dotato di CPU a 8 core, oltre ad una soluzione per server rack basata su due processori della famiglia Naples entrambi dotati al proprio interno di 32 core. Tutti i dettagli su quella prima presentazione sono disponibili online a questo indirizzo.

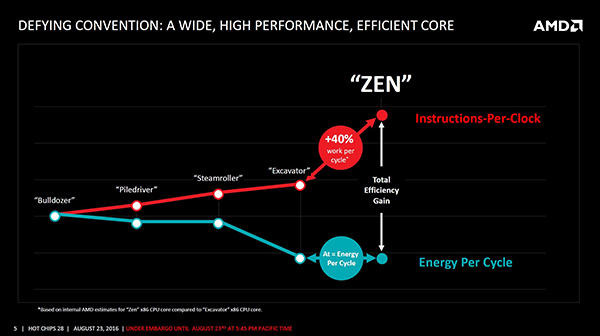

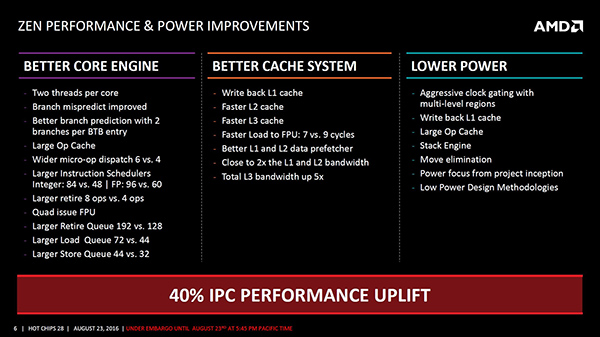

In termini estremamente semplici, con Zen AMD ha l'obiettivo di mettere a disposizione un incremento dell'IPC cioè del numero di istruzioni che vengono processate per ogni ciclo di clock dalla CPU superiore del 40% rispetto a quanto offerto con l'attuale generazione di CPU della famiglia Excavator.

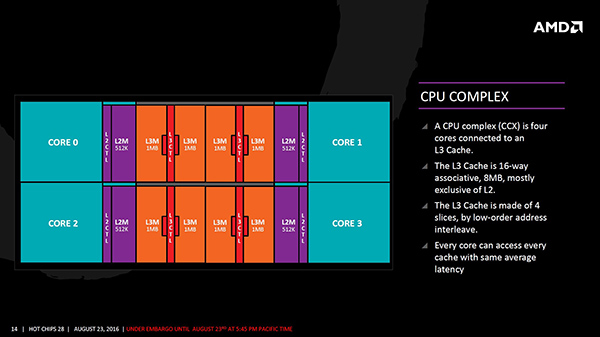

L'architettura alla base prevede l'utilizzo di core che vengono raggruppati 4 per volta in quello che viene definito come CPU-Complex o CCX: in un CCX i 4 core condividono tra di loro una cache L3 da 8 Mbytes di capacità, mentre ogni core è dotato di una propria cache L2. La cache L1 cambia approccio rispetto alle architetture ora in commercio in quanto è di tipo write-back e non più write-through.

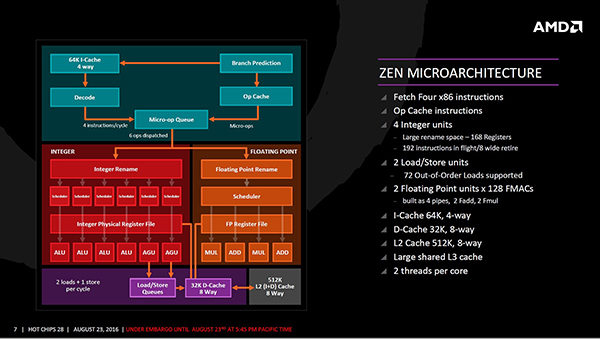

Le prime novità riguardano la parte front end della CPU, nella quale trovano spazio 4 unità di tipo integer con 2 unità per load/store, mentre la componente in virgola mobile è gestita da 2 FMACs a 128bit che possono venir abbinati così da fornire supporto alle istruzioni AVX2 a 256bit. La branch prediction è stata ovviamente migliorata utilizzando per la prima volta in un'architettura AMD una Op cache che velocizza le operazioni di decode delle istruzioni senza che il decoder debba necessariamente passare per la memoria di sistema.

La cache L3 da 8 Mbytes per ogni blocco di 4 core ha un approccio che è simile a quello adottato da Intel per le proprie soluzioni quad core della famiglia Core destinate a sistemi desktop e notebook. La bandwidth della cache L3 è superiore di 5 volte rispetto a quella adottata per le CPU AMD della famiglia Excavator in commercio. Tra le novità di Zen, già segnalate da tempo, evidenziamo il supporto al simultaneous multi-threading: questo permette ad ogni core di gestire in parallelo due thread, che operano di fatto in competizione tra di loro così da sfruttare le risorse a disposizione del sistema al massimo.

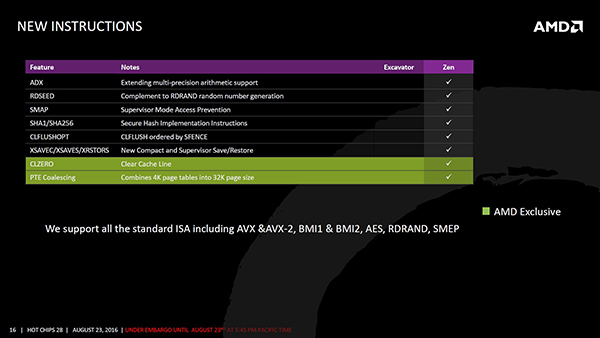

Non manca, a concludere, il set di istruzioni di accelerazione di vari compiti di elaborazione che AMD ha inserito nelle soluzioni Zen. Segnaliamo tra le varie le istruzioni AVX e AVX2, oltre a quelle CLzero e PTE Coalescing che rappresentano delle esclusive per le CPU AMD basate su questa nuova architettura.

Possiamo sintetizzare le informazioni fornite da AMD segnalando come varie migliorie a livello architetturale puntino a fare in modo che il front end della CPU sia sempre occupato nelle elaborazioni contemporaneamente, così che operazioni di tipo ridondante vengano bypassate e in questo modo migliorare l'efficienza complessiva. AMD vuole superare buona parte delle limitazioni incontrate in precedenza con l'architettura Bulldozer di precedente generazione, carente in termini di IPC e non così efficiente nel complesso come le proposte concorrenti di Intel.

In questa fase iniziale AMD non ha fornito indicazioni sulle differenti versioni di processore Zen che verranno presentate al debutto. Ci attendiamo sicuramente una declinazione a 8 core, indicata con il nome di Summit Ridge, oltre a CPU per sistemi server della famiglia Naples dotate al proprio interno di 32 core ciascuna. Nessun dettaglio anche sulle frequenze di clock: sappiamo che il sistema demo mostrato la scorsa settimana in un evento a San Francisco utilizzava processore Summit Ridge con frequenza di clock di 3 GHz. Con l'avvicinarsi del debutto ufficiale sul mercato AMD fornirà ulteriori informazioni sulle soluzioni Zen, completanto quando anticipato la scorsa settimana all'evento di San Francisco e nella presentazione tenuta alla conferenza Hot Chips.

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone'

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone' Appian: non solo low code. La missione è l’ottimizzazione dei processi con l'IA

Appian: non solo low code. La missione è l’ottimizzazione dei processi con l'IA Lenovo ThinkVision 3D 27, la steroscopia senza occhialini

Lenovo ThinkVision 3D 27, la steroscopia senza occhialini  eFootball taglia il traguardo dei 750 milioni di download: al via una campagna in-game

eFootball taglia il traguardo dei 750 milioni di download: al via una campagna in-game MS-DOS 4.0 diventa open source: Microsoft rende disponibile il codice sorgente

MS-DOS 4.0 diventa open source: Microsoft rende disponibile il codice sorgente Micron riceverà 6,1 miliardi di dollari di sussidi dal CHIPS Act americano

Micron riceverà 6,1 miliardi di dollari di sussidi dal CHIPS Act americano STALKER 2 Heart of Chornobyl: nuovo trailer e screenshot

STALKER 2 Heart of Chornobyl: nuovo trailer e screenshot Google: ancora un rinvio per lo stop ai cookie. Per antitrust e privacy non avverrŕ prima del 2025

Google: ancora un rinvio per lo stop ai cookie. Per antitrust e privacy non avverrŕ prima del 2025 Lotus Evija X č la seconda auto elettrica piů veloce al Nürburgring

Lotus Evija X č la seconda auto elettrica piů veloce al Nürburgring NIO e Lotus annunciano una grossa novità: svilupperanno insieme ricarica e scambio batteria

NIO e Lotus annunciano una grossa novità: svilupperanno insieme ricarica e scambio batteria Esclusive PlayStation su Xbox? Sì secondo un insider: Helldivers 2 sarà la prima

Esclusive PlayStation su Xbox? Sì secondo un insider: Helldivers 2 sarà la prima CATL: una nuova batteria per auto elettriche capace di offrire 600 km di autonomia con 10 minuti di ricarica

CATL: una nuova batteria per auto elettriche capace di offrire 600 km di autonomia con 10 minuti di ricarica TikTok al bando negli USA? Biden firma, ByteDance non vuole vendere. La parola ai tribunali

TikTok al bando negli USA? Biden firma, ByteDance non vuole vendere. La parola ai tribunali Taglio di prezzo di 150 euro per SAMSUNG Galaxy S24, S24+ e S24 Ultra: l'S24 si puň adesso acquistare a 649€

Taglio di prezzo di 150 euro per SAMSUNG Galaxy S24, S24+ e S24 Ultra: l'S24 si puň adesso acquistare a 649€ Utenti Amazon Prime: torna a 148€ il mini PC con CPU Intel 16GB/512GB! Per tutti quello da 379€ con AMD Ryzen 7 5700U e 32GB RAM!

Utenti Amazon Prime: torna a 148€ il mini PC con CPU Intel 16GB/512GB! Per tutti quello da 379€ con AMD Ryzen 7 5700U e 32GB RAM! Microsoft sfiora i 62 miliardi di dollari, ottimo trimestre grazie a cloud e Windows

Microsoft sfiora i 62 miliardi di dollari, ottimo trimestre grazie a cloud e Windows Coca-Cola al cloud con un pizzico di IA: stretto un accordo con Microsoft per 1,1 miliardi di dollari

Coca-Cola al cloud con un pizzico di IA: stretto un accordo con Microsoft per 1,1 miliardi di dollari

51 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoPerchè si è visto altro?

Ah no, è vero. C' anche un fimato dell'oste che assaggia il suo vino e dice che è buono come quello dell'altro.

Solito discorso. Si parlerà di roba concreta davanti a dettagliati benchmark comparativi VERI.

Per adesso SLIDE!

Sandy Bridge to Ivy Bridge: Average ~5.8% Up

Ivy Bridge to Haswell: Average ~11.2% Up

Haswell to Broadwell: Average ~3.3% Up

Broadwell to Skylake (DDR3): Average ~2.4% Up

Broadwell to Skylake (DDR4): Average ~2.7% Up

se non sbaglio da Nehalem a SB c'era un +15% MEDIO di IPC.

quindi +40% da excavator non è affatto tanto, è il minimo che potessimo sperare in realtà

Ma se intel sta facendo solo +3% a nuova cpu, come farebbe AMD a fare +40% scusami?

Comunque dovremmo essere vicini al rilascio, magari si scopre che il +40% è il massimo e non il medio, oppure potrebbe essere anche segato dall'ipc int (dove amd andava comunque discretamente) e ritrovarsi con un +20 in calcoli int e +60 in fpu, buh....

Manco un engineering sample..

Comunque dovremmo essere vicini al rilascio, magari si scopre che il +40% è il massimo e non il medio, oppure potrebbe essere anche segato dall'ipc int (dove amd andava comunque discretamente) e ritrovarsi con un +20 in calcoli int e +60 in fpu, buh....

Penso sia proprio così.

Sandy Bridge to Ivy Bridge: Average ~5.8% Up

Ivy Bridge to Haswell: Average ~11.2% Up

Haswell to Broadwell: Average ~3.3% Up

Broadwell to Skylake (DDR3): Average ~2.4% Up

Broadwell to Skylake (DDR4): Average ~2.7% Up

se non sbaglio da Nehalem a SB c'era un +15% MEDIO di IPC.

quindi +40% da excavator non è affatto tanto, è il minimo che potessimo sperare in realtà

normalizzato sulla frequenza (IPC)?

perche' mi sembra davvero tanto su int e FPU, evitando di usare le SIMD.

davo piu' o meno un +15-20%.

per chi invece critica sempre e comunque, se invece di farlo si leggessero le slide, si capirebbe anche il perche'.

l'aumento rispetto ad excavator deriva semplicemente dal fatto che ora usa SMT, e fa' 2 thread simultanei rispetto a uno (in realta' il 40% in piu' non e' probabilmente IPC, ma istruzioni totali, in quanto gira a frequenze piu' basse, di 3/4; diversamente avrebbero la stessa computazione finale tra' un quad ed un octacore).

nulla di piu', nulla di meno di quello che fa' intel da SB.

(e HT non e' SMT, ma si puo' sommare a questo).

di queste slide a me interessa principalmente la parte "Aggresive clock gating with multi-livel regions", che indica probabilmente che se gira con un solo core avra' una frequenza alta, con due un po' piu' bassa, con 4 ancora piu' bassa e con 8 si piazzerà a 2.8/3.2ghz, sempre rimanendo in un power limit dato dal TDP;

con queste premesse in single thread dovrebbe clockare a 4.0ghz per stare dietro ad un 6700K che ragiunge i 4.2 in turbo, a 3.6-3.7 per ugualiarlo in quad thread e anche se facesse 3ghz con tutti gli 8 core attivi, andrebbe il 40% in piu' (ecco la corsa di kaby lake ai 6 core nel mainstream).

non credo che inizialmente saranno quelle le frequenza (piu' propenso a pensare a 2.8x8/3.2x4/3.4x2/3.6x1 per rimanere sotto i 95W nell'uso normale e non sotto torture test, il che lo farebbe confrontare, in perdita, con un 6700), ma... processori a 140W si possono sempre tirare fuori, non sono certo uno scandalo, e una BE uno se la dovrebbe anche aspettare.

in pratica con 4 thread non sfigurerà, ed i monothread sono comunque garantiti con un'esecuzione ai giusti livelli, mentre nei programmi adatti puo' sfruttare tutte le risorse a disposizione, rendendolo molto piu' versatile delle CPU attuali.

se poi si da' retta ai grafici, sapere che a pari frequenza consuma la metà, mentre mantiene la stessa efficienza per ciclo di excavator garantendone il 40% in piu', fa' capire che ci hanno messo il doppio delle cose, e che questa volta sono in grado di usarle come fa' intel (altra cosa che fa' pensare questo e' l'integer rename ed il FPU point rename; a che scopo rinominare istruzioni se non le devi cambiare in qualche modo?)

si puo' vedere Zen come un dual BD, in cui le ALU di un cluster sono state accoppiate dal decode per eseguire 2 istruzioni a ciclo.

è molto chiaro, Zen non è altro che l'architettura Core come approccio, rivista e con aggiunta di tweak vari.

ragazzi fare +40% da 100 è come fare +20% da 200. il risultato è che hai sempre un +40 assoluto.

quindi devi considerare da dove parti, e parti da excavator che è CMT, mentre sandy bridge cos' come Zen sono SMT.

Link ad immagine (click per visualizzarla)

come vedi skylake è +58% MEDIO in ST su excavator.

Vabbe, se non capisci l'ironia non ne ho colpa.

Comunque il valore di ipc è un dato statistico, e non è matematica (come la media di dati)

La statistica non è scienza

perche' mi sembra davvero tanto su int e FPU, evitando di usare le SIMD.

davo piu' o meno un +15-20%.

per chi invece critica sempre e comunque, se invece di farlo si leggessero le slide, si capirebbe anche il perche'.

l'aumento rispetto ad excavator deriva semplicemente dal fatto che ora usa SMT, e fa' 2 thread simultanei rispetto a uno (in realta' il 40% in piu' non e' probabilmente IPC, ma istruzioni totali, in quanto gira a frequenze piu' basse, di 3/4; diversamente avrebbero la stessa computazione finale tra' un quad ed un octacore).

nulla di piu', nulla di meno di quello che fa' intel da SB.

(e HT non e' SMT, ma si puo' sommare a questo).

di queste slide a me interessa principalmente la parte "Aggresive clock gating with multi-livel regions", che indica probabilmente che se gira con un solo core avra' una frequenza alta, con due un po' piu' bassa, con 4 ancora piu' bassa e con 8 si piazzerà a 2.8/3.2ghz, sempre rimanendo in un power limit dato dal TDP;

con queste premesse in single thread dovrebbe clockare a 4.0ghz per stare dietro ad un 6700K che ragiunge i 4.2 in turbo, a 3.6-3.7 per ugualiarlo in quad thread e anche se facesse 3ghz con tutti gli 8 core attivi, andrebbe il 40% in piu' (ecco la corsa di kaby lake ai 6 core nel mainstream).

non credo che inizialmente saranno quelle le frequenza (piu' propenso a pensare a 2.8x8/3.2x4/3.4x2/3.6x1 per rimanere sotto i 95W nell'uso normale e non sotto torture test, il che lo farebbe confrontare, in perdita, con un 6700), ma... processori a 140W si possono sempre tirare fuori, non sono certo uno scandalo, e una BE uno se la dovrebbe anche aspettare.

in pratica con 4 thread non sfigurerà, ed i monothread sono comunque garantiti con un'esecuzione ai giusti livelli, mentre nei programmi adatti puo' sfruttare tutte le risorse a disposizione, rendendolo molto piu' versatile delle CPU attuali.

se poi si da' retta ai grafici, sapere che a pari frequenza consuma la metà, mentre mantiene la stessa efficienza per ciclo di excavator garantendone il 40% in piu', fa' capire che ci hanno messo il doppio delle cose, e che questa volta sono in grado di usarle come fa' intel (altra cosa che fa' pensare questo e' l'integer rename ed il FPU point rename; a che scopo rinominare istruzioni se non le devi cambiare in qualche modo?)

si puo' vedere Zen come un dual BD, in cui le ALU di un cluster sono state accoppiate dal decode per eseguire 2 istruzioni a ciclo.

Non c'ho capito una parola, ma:

Non sappiamo se quel +40% sia riferito all'ipc ST, o all'ipc per core (quindi core0 + core1), alla velocità di clock, al prapporto performance watt, alle pere della nonna o alle banane del fruttivendolo. Si presume che si tratti di ipc (e l'ipc si misura in istruzioni per clock su singolo th) altrimenti potrebbero essere Gflops o qualche altro valore.

Una cosa però che dimentichi di considerare (non so se dimentichi o vuoi coscientemente dimenticare) è che BD aveva 8 core int, ma solo quattro fpu.

Dalle mie parti, ma anche come recitava una vecchia pubblicità, si dice che dos is mejo che one, guia questo da solo dovrebbe permettere un ipc superiore del 25% sul singolo th.

Quindi l'ipc medio in st deve essere almeno il 25% più alto di excavator.

Magari mi sbaglio, sia ben chiaro, ma penso che Intel al contrario dei suoi utenti non dorme tranquilla, sopratutto considerando che (da mie personali fonti interne in intel) gli RMA dei 6700k sono 10 volte superiori a quelle delle precedenti cpu k, segnale che sono al limite superiore della commercializzazione insieme al fatto che nelle prossime cpu contrariamente a quanto immaginabile hanno ulteriormente alzato il tdp (e non facciamo una filippica sul fatto che 97w di tdp potrebbero non essere 97w di dissipazione etc, etc)

La parte in grasseto poi non l'ho capita, ero certo che HT è il nome commerciale (e registrato) che Intel ha dato alla sua implementazione dell'smt.

Sono anni che AMD non fa una cippa sul silicio, ma credo che gli ingegneri IBM abbiamo lavorato sodo e hanno tirato fuori cpu dal loro silicio da far paura a tutti, intel inclusa. E non lavorando su una sola tipologia di cpu ma su diverse di diverso tipo e caratteristiche, cosa che fa pensare che abbiano molta più familiarità sulle implementazioni ad alte prestazioni rispetto quelli di intel.

Guarda caso gli stessi ingegneri e la stessa fonderia (fab 8 Malta ex ibm ora GF) che dovrà produrre ZEN

E che avranno prestazioni più elevate con la metà del prezzo. Io intanto sono arrivato a quest'anno come sempre contento, con il processore in firma e un Phenom II X6 che ancora vanno alla grande e non deludono, e non ho speso 1000€ per una CPU.

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".