Xeon Clearwater Forest, oltre il processo Intel 18A c'è di più

Intel ha svelato molti dettagli sulla CPU Xeon interamente basata su E-core del 2025, nome in codice Clearwater Forest. Il processore unirà tante nuove soluzioni come il processo Intel 18A e le tecnologie di packaging Foveros Direct 3D ed EMIB 3.5D.

di Manolo De Agostini pubblicata il 26 Febbraio 2024, alle 20:31 nel canale ProcessoriIntelClearwater ForestXeon

Nei giorni scorsi sono emersi interessanti dettagli tecnici su Clearwater Forest, nome in codice di un processore Xeon di Intel previsto per il 2025 e interamente basato su E-core. Fondamentalmente, il successore dello Xeon "Sierra Forest" che vedremo debuttare quest'anno.

Intel aveva già reso noto che i core (architettura Darkmont) saranno prodotti con processo Intel 18A, evoluzione di quello 20A che introdurrà, per la prima volta, i nuovi transistor RibbonFET e l'alimentazione dal retro dei transistor PowerVia.

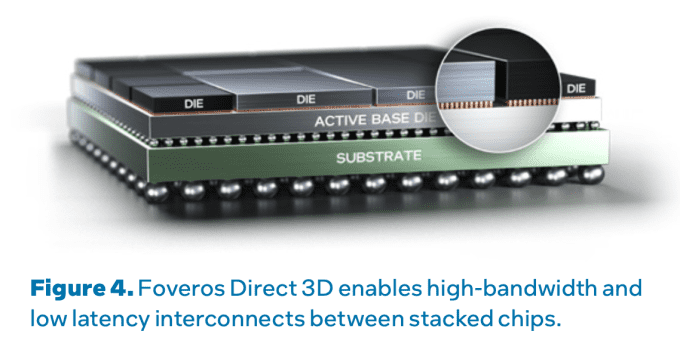

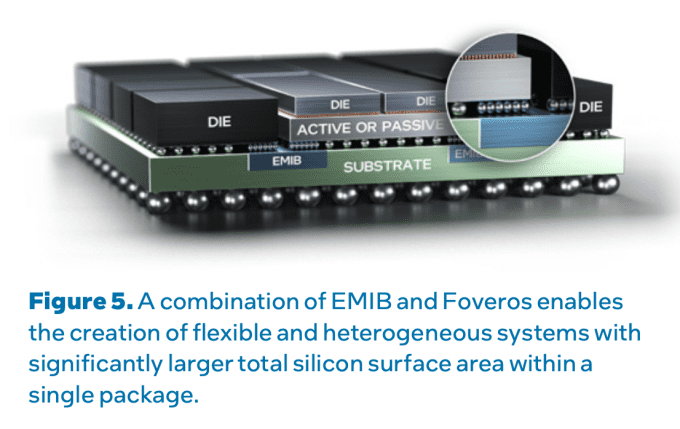

Questa però è solo una delle innovazioni del progetto Clearwater Forest, perché vedremo per la prima volta un package avanzato basato su due tecnologie chiamate Foveros Direct 3D e EMIB 3.5D. La prima consente ai chiplet impilati di essere collegati verticalmente in modo molto ravvicinato e consentire una bandwidth elevata.

Foveros Direct 3D si basa sul cosiddetto "hybrid bonding" tra i punti di contatto di ciascun chip. Le interconnessioni elettriche verticali in rame vengono allineate tra loro, operazione che Intel descrive come "collegamento a termocompressione dei collegamenti verticali in rame". Qualcosa di simile alla tecnologia SoIC di TSMC che viene usata da AMD per la 3D V-Cache sulle CPU Ryzen.

Secondo Intel, Foveros Direct 3D può essere usato sia "face to face" che "face to back". È anche possibile utilizzare wafer e chip di diversi produttori. La prima generazione di Foveros Direct 3D consentirà distanze tra i punti di saldatura (bump) di 9 µm. La generazione successiva scenderà a 3 µm.

Per la connessione tramite Foveros Direct 3D, Intel produrrà il die base di Clearwater Forest con processo Intel 3-T, una delle nuove tecnologie annunciate all'IFS Direct Connect. Nel suo documento, Intel parla della presenza di una cache locale nel die di base, che si aggiungerà a quella presente nella Compute Tile. Non è la prima volta che Intel integra una cache nella Base Tile, l'ha già fatto con l'acceleratore HPC Ponte Vecchio.

Per quanto riguarda EMIB 3.5D, si tratta della combinazione di EMIB e Foveros, ma le due tecnologie rappresentano due fasi e tecniche di processo separate. La seconda generazione di EMIB ridurrà il bump pitch da 55 a 45 µm.

Durante IFS Direct Connect 2024 l'amministratore delegato Pat Gelsinger ha mostrato un chip preliminare di Clearwater Forest, con le due Compute Tile al centro e due I/O Tile ai lati, in modo simile ai progetti Sierra Forest e Granite Rapids al debutto quest'anno.

Attenti a Poco F7: può essere il best buy del 2025. Recensione

Attenti a Poco F7: può essere il best buy del 2025. Recensione Recensione Samsung Galaxy Z Fold7: un grande salto generazionale

Recensione Samsung Galaxy Z Fold7: un grande salto generazionale  The Edge of Fate è Destiny 2.5. E questo è un problema

The Edge of Fate è Destiny 2.5. E questo è un problema Cooler Master MasterFrame 360 Panorama S Limited Edition: solo 100 pezzi al mondo

Cooler Master MasterFrame 360 Panorama S Limited Edition: solo 100 pezzi al mondo Motorola e Swarovski lanciano The Brilliant Collection con cristalli Swarovski

Motorola e Swarovski lanciano The Brilliant Collection con cristalli Swarovski Wikipedia dichiara guerra all'IA spregiudicata: cancellazione rapida per gli articoli non revisionati

Wikipedia dichiara guerra all'IA spregiudicata: cancellazione rapida per gli articoli non revisionati Dai social ai farmaci dimagranti: il nuovo incarico della ex CEO di X (Twitter)

Dai social ai farmaci dimagranti: il nuovo incarico della ex CEO di X (Twitter) Addio spam su WhatsApp? Ecco le nuove difese contro l'aggiunta indesiderata nei gruppi

Addio spam su WhatsApp? Ecco le nuove difese contro l'aggiunta indesiderata nei gruppi Su Windows 11 25H2 cambierà (in peggio?) la gestione dei collegamenti sul desktop

Su Windows 11 25H2 cambierà (in peggio?) la gestione dei collegamenti sul desktop Per la prima volta un portatile gaming con RTX 5060 a 999: è un HP Victus, ottimo anche come tuttofare

Per la prima volta un portatile gaming con RTX 5060 a 999: è un HP Victus, ottimo anche come tuttofare Meta condannata per aver violato la privacy delle donne: raccoglieva dati su mestruazioni e gravidanze

Meta condannata per aver violato la privacy delle donne: raccoglieva dati su mestruazioni e gravidanze Hai almeno 16GB di RAM? Ecco il nuovo modello di OpenAI che puoi installare subito

Hai almeno 16GB di RAM? Ecco il nuovo modello di OpenAI che puoi installare subito Proxmox annuncia Proxmox VE 9.0: Debian 13, snapshot su iSCSI e nuove funzionalità di SDN tra le novità

Proxmox annuncia Proxmox VE 9.0: Debian 13, snapshot su iSCSI e nuove funzionalità di SDN tra le novità IA agentica: i modelli di sicurezza tradizionali non bastano più. Serve cambiare approccio. Il punto di vista di Reply

IA agentica: i modelli di sicurezza tradizionali non bastano più. Serve cambiare approccio. Il punto di vista di Reply  One UI 8 beta in arrivo su Galaxy S24 e altri modelli: la lista completa dei dispositivi compatibili

One UI 8 beta in arrivo su Galaxy S24 e altri modelli: la lista completa dei dispositivi compatibili Trimestre record per AMD: le Radeon RX 9000 sono un successo, ma la Cina punisce

Trimestre record per AMD: le Radeon RX 9000 sono un successo, ma la Cina punisce Furti di auto in aumento: 136 mila veicoli spariti nel 2024, auto vecchie da 4 a 6 anni a maggior rischio

Furti di auto in aumento: 136 mila veicoli spariti nel 2024, auto vecchie da 4 a 6 anni a maggior rischio

0 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoDevi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".