Fare calcoli dentro una memoria, Samsung ci riesce per la prima volta con una MRAM

Samsung ha presentato la prima applicazione di "in-memory computing" al mondo basata su MRAM. In parole povere, un chip di memoria MRAM è riuscito a svolgere calcoli complessi, senza necessitare di un processore separato.

di Manolo De Agostini pubblicata il 13 Gennaio 2022, alle 06:41 nel canale MemorieSamsung

Samsung ha dimostrato, per la prima volta al mondo, che è possibile svolgere calcoli all'interno di una MRAM (Magnetoresistive Random Access Memory). Il cosiddetto "in-memory computing" è al centro di uno studio pubblicato su Nature intitolato "A crossbar array of magnetoresistive memory devices for in-memory computing", guidato dal Samsung Advanced Institute of Technology (SAIT) in stretta collaborazione con il Samsung Electronics Foundry Business e il Semiconductor R&D Center.

La novità cambia il modo in cui vediamo l'architettura di calcolo standard, dove i chip di memoria hanno la mera funzione di archiviazione dei dati (temporanea o duratura nel tempo), mentre dei processori separati (CPU, GPU, ecc.) prendono queste informazioni e le processano. L'in-memory computing prevede invece che la memoria abbia una doppia funzione, oltre a quella di archiviazione anche quella di calcolo.

(Da sinistra) Dr. Donhee Ham, Fellow del SAIT e professore della Harvard University, Dr. Seungchul Jung, Staff Researcher presso il SAIT e Dr. Sang Joon Kim, Vice President of Technology del SAIT

L'obiettivo è chiaro: processare i dati senza spostarli, in modo da farlo in modo rapido (l'elaborazione avviene in modo parallelo) e con consumi decisamente inferiori. "L'in-memory computing", spiega Samsung "è quindi una delle tecnologie promettenti che permetteranno di creare chip di intelligenza artificiale a bassa potenza di prossima generazione".

Finora molte ricerche sull'in-memory computing si erano concentrate su due tipi di soluzioni non volatili, RRAM (Resistive Random Access Memory) e PRAM (Phase-change Random Access Memory), in quanto nonostante la MRAM avesse indubbie qualità - velocità, resistenza e produzione su larga scala - evidenziava problemi legati alla bassa resistenza della memoria stessa.

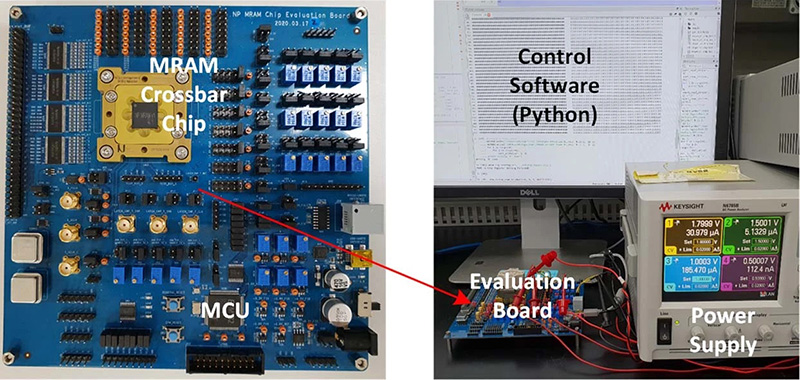

A sinistra una scheda di prototipazione con regolatori di tensione, generatori di clock, una MCU e il chip MRAM. A destra uno scatto che mostra come la MCU comunichi con il PC via USB

I ricercatori di casa Samsung sono riusciti a superare quell'ostacolo mettendo a punto una MRAM "differente", composta da più layer (si parla di un array), in cui l'architettura di in-memory computing anziché essere basata sulla somma delle correnti è basata sulla somma delle resistenze, andando così a "risolvere il problema delle piccole resistenze dei singoli dispositivi MRAM".

L'azienda sudcoreana ha successivamente testato le prestazioni di questa MRAM con operazioni di intelligenza artificiale, rilevando una precisione del 98% nella classificazione delle cifre scritte a mano e una precisione del 93% nel rilevamento dei volti.

Non solo, i ricercatori ritengono che questo nuovo chip MRAM possa fungere anche da piattaforma per "scaricare" reti neuronali biologiche, una possibilità in linea con la visione dell'azienda in merito all'elettronica neuromorfica condivisa da Samsung lo scorso settembre.

"L'elaborazione in memoria ha somiglianze con il cervello, nel senso che nel cervello il calcolo si verifica anche all'interno della rete di memorie biologiche, o sinapsi, i punti in cui i neuroni si toccano", ha affermato il dott. Seungchul Jung, il primo autore dell'articolo. "In effetti, mentre l'elaborazione eseguita dalla nostra rete MRAM per ora ha uno scopo diverso dal calcolo svolto dal cervello, tale rete di memoria a stato solido potrebbe essere usata in futuro come piattaforma per imitare il cervello modellando la connettività delle sinapsi".

Idrogeno verde in Europa: nuovi studi prevedono costi ben superiori alle aspettative

Idrogeno verde in Europa: nuovi studi prevedono costi ben superiori alle aspettative Mario Kart World lancia Switch 2: la magia Nintendo ora in 4K

Mario Kart World lancia Switch 2: la magia Nintendo ora in 4K La rivoluzione dei dati in tempo reale è in arrivo. Un assaggio a Confluent Current 2025

La rivoluzione dei dati in tempo reale è in arrivo. Un assaggio a Confluent Current 2025 Come sfruttare le offerte di Amazon per potenziare il PC: sconti su schede video GeForce e Radeon, CPU Intel e AMD, monitor, SSD, memorie e molto altro

Come sfruttare le offerte di Amazon per potenziare il PC: sconti su schede video GeForce e Radeon, CPU Intel e AMD, monitor, SSD, memorie e molto altro AirPods, rivoluzione in arrivo: controllo fotocamera, rilevamento sonno e gesture evolute

AirPods, rivoluzione in arrivo: controllo fotocamera, rilevamento sonno e gesture evolute  ECOVACS DEEBOT T50 PRO OMNI -22%: recente, completo e scontato, con 15.000Pa e lavaggio ad acqua calda

ECOVACS DEEBOT T50 PRO OMNI -22%: recente, completo e scontato, con 15.000Pa e lavaggio ad acqua calda Scopa elettrica, super accessoriata e potentissima (45KPa), crolla di prezzo con un coupon, solo 109

Scopa elettrica, super accessoriata e potentissima (45KPa), crolla di prezzo con un coupon, solo 109 Aruba collabora con Microsoft per l'offerta Azure Local

Aruba collabora con Microsoft per l'offerta Azure Local Shimano Q'AUTO: cambio elettronico automatico che si adatta al ciclista, senza batteria!

Shimano Q'AUTO: cambio elettronico automatico che si adatta al ciclista, senza batteria! The Witcher 4: la demo mostrata all'Unreal Fest non è rappresentativa del gioco

The Witcher 4: la demo mostrata all'Unreal Fest non è rappresentativa del gioco Pornhub e YouPorn oscurati in Francia: Aylo contesta le nuove regole sull'identità digitale

Pornhub e YouPorn oscurati in Francia: Aylo contesta le nuove regole sull'identità digitale Audio immersivo con altoparlanti posizionati a caso? Ora è possibile con TCL FlexConnect

Audio immersivo con altoparlanti posizionati a caso? Ora è possibile con TCL FlexConnect Mercedes G580 EQ in difficoltà: l'elettrico non scalda il pubblico dei fuoristrada di lusso

Mercedes G580 EQ in difficoltà: l'elettrico non scalda il pubblico dei fuoristrada di lusso CATL: la ricerca sulle batterie al litio-metallo prosegue, vicina all'applicazione per EV e aerei

CATL: la ricerca sulle batterie al litio-metallo prosegue, vicina all'applicazione per EV e aerei SteelSeries Arctis Nova Pro Wireless: il top per il gaming e non solo. Recensione

SteelSeries Arctis Nova Pro Wireless: il top per il gaming e non solo. Recensione  iPhone 17, il display sarà finalmente a 120Hz ma non ProMotion: cosa significa

iPhone 17, il display sarà finalmente a 120Hz ma non ProMotion: cosa significa NIO prepara l'esordio in sette nuovi mercati europei entro il 2026

NIO prepara l'esordio in sette nuovi mercati europei entro il 2026

10 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoNon capisco questo punto, che centra la precisione del riconoscimento con l'architettura hardware? Se io implemento un ottimo algoritmo di riconoscimento usando bicchieri e acqua, significa forse che questa architettura é buona?

Non capisco questo punto, che centra la precisione del riconoscimento con l'architettura hardware? Se io implemento un ottimo algoritmo di riconoscimento usando bicchieri e acqua, significa forse che questa architettura é buona?

Hanno solo detto che processando i dati direttamente in memoria hanno ottenuto quei risultati, quindi comparabili alle soluzioni classiche. L'idea è davvero interessante, anche se mi piacerebbe vedere dei confronti in termini di tempo di esecuzione rispetto all'esecuzione su CPU classica.

Non capisco questo punto, che centra la precisione del riconoscimento con l'architettura hardware? Se io implemento un ottimo algoritmo di riconoscimento usando bicchieri e acqua, significa forse che questa architettura é buona?

Una nuova architettura hw potrebbe richiedere l'implementazione di una nuova gestione degli errori quindi credo che come confronto ci stia.

Chiedo il parere degli esperti, ma poter eseguire operazioni direttamente nelle memorie credo che amplii di molto le possibilità di attacchi.

Chiedo il parere degli esperti, ma poter eseguire operazioni direttamente nelle memorie credo che amplii di molto le possibilità di attacchi.

Potenzialmente esisono due scenari possibili a seconda che queste operazioni vengano effettuate una-tantum, oppure si parli di programmi persistenti in RAM.

In entrambi i casi, è ipotizzabile che la RAM venga vista come un co-processore, nel senso che dal mio punto di vista si può pensare che debba essere sempre la CPU principale a dover caricare le istruzioni da eseguire, ipotizziamo in un linguaggio ad-hoc e comunque per effettuare operazioni limitate (es. XOR, ADD, SUB?), possibilmente *SENZA* cicli. Bisognerà anche vedere se inizialmente non si consideri il solo accesso in lettura senza possibilità di modificare i dati, magari con l'output memorizzato in aree buffer separate (tipo una piccola SRAM on-board).

Nota: già oggi esistono alcuni controller DMA nel mondo embedded che sono programmabili con istruzioni ad-hoc secondo il modello descritto in precedenza.

In aggiunta a questo si può pensare a qualcosa simile al modello di calcolo delle GPU (es. CUDA, OpenCL):

a) l'host (CPU) carica (copia) i dati sulla GPU

b) l'host (CPU) avvia il programma sulla GPU

c) l'host (CPU) recupera (copia) i dati elaborati dalla GPU

Questo scenario mi preoccupa relativamente poco perché non esiste un programma sempre "persistente" in esecuzione sul co-processore (anche se tecnicamente è assolutamente possibile farlo, ad esempio sulle GPU basta porre i kernel in ciclo infinito, con le giuste accortezze).

La domanda più importante è se sarà possibile usare gli indirizzi in queste ipotetiche istruzioni oppure banalmente l'host specificherà una volta per tutte il range di indirizzi su cui operare.

Questo naturalmente cambia notevolmente la sicurezza. Se posso usare indirizzi fisici arbitrari nel "programma RAM", chi garantisce la protezione della memoria e l'isolamento tra le applicazioni?

Si tenga presente che ad oggi è la CPU attraverso la MMU che converte gli indirizzi virtuali (quelli che compaiono nelle istruzioni) in indirizzi fisici (quelli messi sul bus degli indirizzi per accedere alla cella di RAM corrispondente), sulla base di tabelle preparate dal SO (page table). Per cui il SO garantisce l'isolamento tra le applicazioni perché l'hardware gli consente di farlo.

È chiaro secondo me che almeno inizialmente il modello di calcolo sarà molto semplificato, e che l'host dovrà, attraverso apposite interfacce, specificare su quali indirizzi operare.

Anche perché ipotizzare un programma persistente in RAM per quanto affascinante richiederebbe anche di revisionare il modello di concorrenza attuale. L'ipotesi classica è che un core singolo legga ciò che ha scritto in RAM. Se questa ipotesi decade perché un "programma RAM" può modificare i dati nella RAM stessa, chiaramente si apre un vaso di pandora

Ma quando si crea un disco RAM, non siamo già nel caso di programma persistente in memoria?

Ci gira Crysis?

Forse mi sono spiegato male, ma capisco che in effetti la cosa può confondere

In questa notizia si parla di chip di RAM che hanno integrata della logica per effettuare computazione (come se avessi dei micro-processori embedded nei chip di RAM).

Queste unità di calcolo *integrate sulla RAM* devono essere in qualche modo "programmate". Ergo quando parlo di "programma RAM" devi pensare al codice/firmware di un micro-controllore integrato sulle RAM.

Diverso dai programmi CPU tradizionali (le cui istruzioni sono presenti in RAM, ma come "semplici" dati)

Nel caso di un RAM-disk, in quel caso hai solo una porzione di RAM con dei dati che vengono interpretati dal SO come un disco, con relativo file system.

La differenza è che allo stato attuale in RAM esistono solo dei dati "passivi" che devono essere recuperati dalla CPU, elaborati nella CPU e riscritti in RAM, mentre nel caso oggetto della news parliamo di RAM "intelligenti" che possono anche effettuare calcoli direttamente.

Ripeto capisco che la cosa può risultare in effetti confusionaria, spero di aver chiarito un pochino.

Si ok, adesso mi torna. Ad ogni modo, immagino che quando si fa ricerche di questo tipo, in parallelo si pensi anche alla sicurezza, altrimenti sarebbero di fatto inutili.

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".