|

|||||||

|

|

|

|

|

|

Strumenti |

|

|

#101 | |

|

Senior Member

Iscritto dal: Sep 2003

Città: Torino

Messaggi: 20953

|

Quote:

cappalo a 65W da bios |

|

|

|

|

|

|

#102 |

|

Moderatore

Iscritto dal: Mar 2007

Messaggi: 22646

|

Il N3P di zen6, avrà un 12% perf/watt /0,75v, quindi è probabile che permetta un aumento di clock finale.

__________________

Ryzen 5800x3D - Msi B450TH - Corsair 32gb 3600 lpx - Red Devil RX 9070XT - samsung 860 pro 1tb - 4tb storage - Acer g-sync xb270hu - AOC CU34G2XPD - MSI MPG A850G atx3.0 |

|

|

|

|

|

#103 | |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 31872

|

Quote:

--------------------------------------------------- A grandi linee, con Zen5, la gestione delle frequenze è gestita così: Frequenza max MT con carico su tutti i core dipende dal PPT max, e se si aumenta il PPT max, subentra la Fmax. La frequenza max turbo entra in funzione (circa) quando PPT e core utilizzati sono meno del 50% (esempio 100W PPT max e si è sui 50W ed, idem, CCX X8 con 4 core spenti)... La stessa logica, applicata al CCX X12, comporterebbe 6 core in turbo vs 4 del CCX X8... e sarebbe più facile vedere un Zen6 in game con tutti i core in turbo rispetto ad un Zen5. Inoltre... in condizione def, AMD imposterà valori TDP di Zen6 uguali a Zen5, in primis perchè se vero che Nova raddoppierà il core count, AMD non ha margine per diminuirlo, e secondo, perchè TDP def superiori a 170W TDP obbligherebbero a cambiare mobo. Il problema è se già un 9950X X16 dai 200W PPT def può arrivare tranquillamente a 300W, un X24 sempre a 200W PPT praticamente sarebbe in ECO MODE

__________________

9950X PBO 1X CO -33 Override +100 CPU-Z RS/DU 930/18.563 - CB23-2339 - 47682 47728 -CB24 144 2508 - OCCT - V-RAY 53.994 - GeekBench 6.3 3563/22664 - TEST RS Y-Cruncher BKT - core 0-15 NPbench - CO -50 + CS -10 (NO RS) CPU-Z-18989 - CB23 48679 - CB24 2593 Ultima modifica di paolo.oliva2 : 02-07-2025 alle 05:16. |

|

|

|

|

|

|

#104 | |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 31872

|

Quote:

A me lascia interdetto il rumor che AMD voglia arrivare a X192 con Epyc Zen6 (non denso), possibile solamente con chiplet X16 (max 12 chiplet CCX X12 = X144, CCX X16 = X192), perchè ciò sarebbe possibile solamente sul 2nm. A mio parere tutto dipende da quale PP AMD utilizzerà per Zen6 Epyc. Per certo è impossibile che AMD realizzi un Chiplet a 2nm per desktop se gli Epyc Zen6 fossero a 3nm, ma sarebbe altrettanto impossibile che AMD realizzi un chiplet specifico Zen6 a 3nm se gli Epyc Zen6 fossero sul 2nm. Se diamo per vero un Nova X52 sul 2nm, avrebbe poco senso (ed anche rischioso commercialmente) un Zen6 sul 3nm e come max X24, perchè in MT riuscire a competere con Nova con un core-count inferiore sommato ad un nodo inferiore, sarebbe la medesima situazione Intel passata, che di certo non era ottimale. Un Chiplet a 2nm Epyc Zen6, nelle varianti X12 e X16, darebbe anche la possibilità ad AMD di portare l'offerta Zen6 desktop a X32. Il "naturale" di questi anni ha visto gli X16 AMD contrapposti all'ibrido Intel X8+X16 (Raptor/Arrow). Verrebbe spontaneo ipotizzare che un passaggio Intel da X8+X16 a X16+X32+X4 non possa vedere AMD fermarsi a X24 da X16... anche perchè un Nova X52 sarebbe indigesto per l'offerta AMD MT, posizionandosi nel mezzo come alternativa nello spazio tra AM5 e Threadripper... difficile, per me, che AMD lo permetta.

__________________

9950X PBO 1X CO -33 Override +100 CPU-Z RS/DU 930/18.563 - CB23-2339 - 47682 47728 -CB24 144 2508 - OCCT - V-RAY 53.994 - GeekBench 6.3 3563/22664 - TEST RS Y-Cruncher BKT - core 0-15 NPbench - CO -50 + CS -10 (NO RS) CPU-Z-18989 - CB23 48679 - CB24 2593 Ultima modifica di paolo.oliva2 : 02-07-2025 alle 09:22. |

|

|

|

|

|

|

#105 | |

|

Moderatore

Iscritto dal: Mar 2007

Messaggi: 22646

|

Quote:

Ero rimasto, ad Epyc 256 core su 8 CCD da 32 core ciascuno /2mb l3, progettato sul 2nm, il chip post torino, attualmente l'unico ad utilizzare il n3E. Riguardo Epyc zen6, si parla sempre di 8 CCD da 96 core (12x8). Non sono del tutto sicuro che si spingerà tanto sulle frequenze, salvo non aumentino ancora i TDP, gli ultimi rumour di intel parlano i 11% ST, ovvero clock e IPC, quindi ben poca cosa, ed AMD non farà molto di più. Si punterà soprattutto ad equilibrare i 24 core, che sono il 50% in più rispetto ai 16.

__________________

Ryzen 5800x3D - Msi B450TH - Corsair 32gb 3600 lpx - Red Devil RX 9070XT - samsung 860 pro 1tb - 4tb storage - Acer g-sync xb270hu - AOC CU34G2XPD - MSI MPG A850G atx3.0 |

|

|

|

|

|

|

#106 |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 31872

|

Ma il vero salto sarebbe nell'MT.

l'intero sistema Zen6 X24 (mobo, CPU, DDR5, ecc.) costerebbe meno della sola CPU Threadripper di uguale prestazione di pochi anni fa, esempio Zen3 X64, e con meno consumo. Inoltre l'aumento del core-count allunga la vita del sistema... perchè un Zen6 X24 sarà valido prestazionalmente e anche lato efficienza vs Zen7 a core-count inferiori (tipo X12).

__________________

9950X PBO 1X CO -33 Override +100 CPU-Z RS/DU 930/18.563 - CB23-2339 - 47682 47728 -CB24 144 2508 - OCCT - V-RAY 53.994 - GeekBench 6.3 3563/22664 - TEST RS Y-Cruncher BKT - core 0-15 NPbench - CO -50 + CS -10 (NO RS) CPU-Z-18989 - CB23 48679 - CB24 2593 |

|

|

|

|

|

#107 | |

|

Moderatore

Iscritto dal: Mar 2007

Messaggi: 22646

|

Quote:

In più c'è l'IPC pensato per gli Epyc, e finalmente l'I/O ridisegnato a 4nm.

__________________

Ryzen 5800x3D - Msi B450TH - Corsair 32gb 3600 lpx - Red Devil RX 9070XT - samsung 860 pro 1tb - 4tb storage - Acer g-sync xb270hu - AOC CU34G2XPD - MSI MPG A850G atx3.0 |

|

|

|

|

|

|

#108 |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 31872

|

Lato IOD, c'è qualche cosa che penalizza Zen5 (in OC) l'aver riciclato l'IOD di Zen4.

L'ho già scritto, ma non c'è spiegazione (per me) del perchè, a parità di frequenza finale, si ottiene un RS occando il bus arrivando a frequenze core ben più alte, impossibili anche solamente da raggiungere con bus def. Poi ovvio, il passaggio al 4nm permetterà frequenze IF + MC/DDR maggiori, ma si parla anche di dimezzamento dei tempi inter-L3 con 2 chiplet, perchè Zen6 dovrebbe inserire un collegamento tra le L3 di 2 chiplet evitando di passare per l'IOD. Comunque... se per "logica" e costi Zen6 dovrebbe utilizzare l'N3P, c'è anche da valutare la durata del socket AM5 in commercio, perchè il socket AM6 e relativo Zen7, arriveranno ALMENO 18 mesi dopo l'uscita di Zen6, quindi si parlerebbe di un Zen6 sul mercato fino a metà 2017 se Zen6 fosse commercializzato a gennaio 2026, ma nel caso di un Zen6 a metà 2016, dovrebbe arrivare al 2018, e sono tanti per un N3P, non solamente per il discorso desktop, ma ancor più lato Strix, che ora arriva ad una iGPU 40CU sul 4nm, ma l'ambizione AMD è ovvio che sia quella di alzare il livello della iGPU, per sempre più sistemi che non richiedano una VGA esterna... il che vuol dire + utile per AMD (costa meno produrre un APU con VGA "tosta" rispetto allo stesso con una VGA discreta a parte della stessa prestazione), costa meno per l'OEM la progettazione della mobo, costa meno l'assemblaggio e costa pure meno il magazzino. Se già di suo sarebbe discutibile utilizzare un 3nm al posto di un 2nm, perchè il 2nm con maggiore densità e maggiore efficienza consentirebbe margini ben maggiori, sarebbe pure gambizzare gli Halo. Ovviamente 18 mesi non sono un lasso di tempo tale da permettere alla concorrenza di commercializzare un qualche cosa stile Halo, ma sufficienti a produrre una VGA discreta mobile che sul 2nm sarebbe più efficiente/prestazionale e quindi ridimensionare Halo, e probabilmente inciderebbe anche sul disorso AI. A che pro?

__________________

9950X PBO 1X CO -33 Override +100 CPU-Z RS/DU 930/18.563 - CB23-2339 - 47682 47728 -CB24 144 2508 - OCCT - V-RAY 53.994 - GeekBench 6.3 3563/22664 - TEST RS Y-Cruncher BKT - core 0-15 NPbench - CO -50 + CS -10 (NO RS) CPU-Z-18989 - CB23 48679 - CB24 2593 Ultima modifica di paolo.oliva2 : 04-07-2025 alle 09:40. |

|

|

|

|

|

#109 |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 31872

|

AMD Ryzen 11000 X3D: Zen 6 spinge la cache a 240 MB

Il rumor non riporta qualcosa di effettivamente nuovo, a parte la dimensione della L3 3D... però "corregge" il nodo con cui sarebbe prodotto Zen6 desktop con una tempistica credibile. Zen6 sarebbe previsto per fine 2026 (e non più inizio 2026), e sul nodo N2X. TSMC dichiara la disponibilità della produzione in volumi a partire da metà 2026 per l'N2P e nel 2027 per l'N2X. Quindi Zen6 rientrerebbe nel credibile per fine 2026 sull'N2P, e non sarebbe neanche da scartare l'N2X, in quanto riportato nel 2027, e sarebbe compatibile con una svendita Zen5 nel periodo natalizio, la presentazione di Zen6 al CES (i primi di gennaio 2027) ed una commercializzazione a seguire, febbraio/marzo/aprile. https://www.ceotech.it/amd-ryzen-110...ache-a-240-mb/

__________________

9950X PBO 1X CO -33 Override +100 CPU-Z RS/DU 930/18.563 - CB23-2339 - 47682 47728 -CB24 144 2508 - OCCT - V-RAY 53.994 - GeekBench 6.3 3563/22664 - TEST RS Y-Cruncher BKT - core 0-15 NPbench - CO -50 + CS -10 (NO RS) CPU-Z-18989 - CB23 48679 - CB24 2593 |

|

|

|

|

|

#110 |

|

Senior Member

Iscritto dal: Aug 2002

Città: Milano

Messaggi: 4634

|

più realistico.

__________________

| Intel 13700k p57r48 HT off | MSI z690 Unify-X | EK AIO-360 RGB | 32GB ddr5 7200@7600 MT | RTX 4080 Super | Optane 900p 280GB + WD SN850X 1TB + Crucial P5 plus 2TB | bequiet! Dark Base 700 white | Asus Loki 850W white | LG 34GN850-B 34" UWQHD | Fibra 1000/300 | |

|

|

|

|

|

#111 | |

|

Senior Member

Iscritto dal: Nov 2023

Città: AUDI RS3

Messaggi: 1592

|

Quote:

__________________

PC1-i5 13600KF-Sapphire rx9070xt Pulse 16gb-MSI PRO Z790-P WIFI-32GB DDR 5 @6000-NVME 1TB Corsair MP600gs-LG OLED 42 C2 PC2-i7 12700-ZOTAC TwinEdge RTX 4070 12gb-GB B760M DS3H DDR4-32GB DDR 4 3200-NVME 1TB Lexar NM620-LG OLED 77 C1 DENON AVR-X2700H 7.2-CASSE KLIPSCH RF52II-PS5 e PSVR 2-Xbox Series X-Nintendo Switch 1 e 2

|

|

|

|

|

|

|

#112 |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 31872

|

Qui viene riportato che AMD ufficialmente avrebbe dichiarato Zen6 Epyc (Zen6 non Zen6C) arriverà a 256 core e prodotto sul 2nm.

https://www.computerbase.de/news/pro...-bieten.93400/ Ovviamente è una notizia che andrebbe confermata... ma se risultasse fondata, diventerebbe relativamente difficile ipotizzare un chiplet Zen6 desktop su un altro PP (3nm). 1) In primis una stesura doppia (3nm e 2nm per Zen6) raddoppierebbe i costi ben più del risparmio in sè lato costo silicio die. 2) La resa fa parte dell'affinamento PP, e questa sale proporzionatamente al volume prodotto. Ottenere lo stesso volume con 2 PP differenti, significherebbe ottenere rese inferiori e/o tempi superiori, ovviamente ben più rapido da ottenere con un unico PP e unico volume. 3) Zen X desktop da sempre viene realizzato con i chiplet che non superano la selezione Epyc in primis e Threadripper poi... che fine farebbe questo silicio? Oltre a tutti questi aspetti negativi, indubbiamente un chiplet Zen6 desktop sul 2nm vs 3nm, garantirebbe frequenze superiori a parità di consumo e/o prestazioni maggiori a parità di consumo/consumi inferiori a parità di prestazione. L'aumento della L3/L3 3D (si parla sino a 240MB), mi pare incoerente con il game (AMD continua a riportare che l'avere 2 chiplet 3D comporterebbe vantaggi pressochè nulli nel game), ma sarebbe un discorso valido nel caso di un Zen6 desktop > X24, perchè l'avere una L3 3D maggiore in ambo i chiplet, se non valida in game, rimarrebbe valida (molto valida) nel caso esempio di X32 in connubio a non essere obbligati a DDR5 con banda (e costi) top.

__________________

9950X PBO 1X CO -33 Override +100 CPU-Z RS/DU 930/18.563 - CB23-2339 - 47682 47728 -CB24 144 2508 - OCCT - V-RAY 53.994 - GeekBench 6.3 3563/22664 - TEST RS Y-Cruncher BKT - core 0-15 NPbench - CO -50 + CS -10 (NO RS) CPU-Z-18989 - CB23 48679 - CB24 2593 Ultima modifica di paolo.oliva2 : 06-07-2025 alle 15:46. |

|

|

|

|

|

#113 | |

|

Moderatore

Iscritto dal: Mar 2007

Messaggi: 22646

|

Quote:

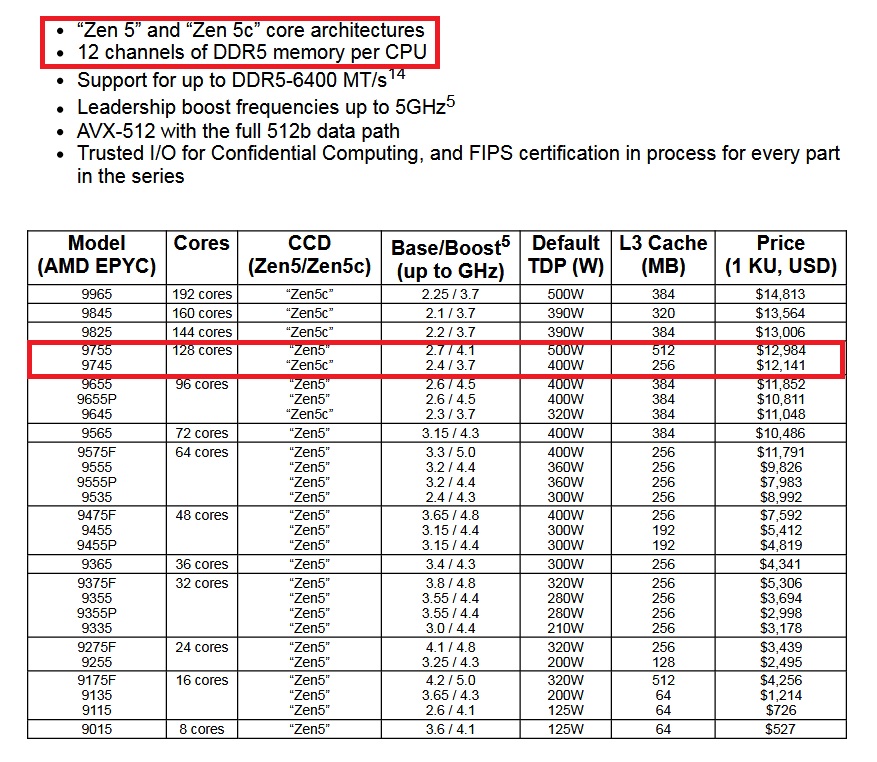

8 CCD su zen6 classico portano a 96 core. Come li suddividi 256 core su CCD da 12? Riguardo il PP, potrebbe anche essere a 2nm, ma già ora abbiamo zen5 sui 4nP e zen5c sui 3nE.

__________________

Ryzen 5800x3D - Msi B450TH - Corsair 32gb 3600 lpx - Red Devil RX 9070XT - samsung 860 pro 1tb - 4tb storage - Acer g-sync xb270hu - AOC CU34G2XPD - MSI MPG A850G atx3.0 |

|

|

|

|

|

|

#114 | |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 31872

|

Quote:

L'offerta Epyc Zen5 offre fino a 192 core con Zen5C prodotto sul 3nm (N3E) e fino a 96 core con Zen5 prodotto sull'N4P, ovvero Zen5C 2X i core di Zen5. Visto che Zen6C pare verrà offerto a 256 core, a specchio Zen5 AMD Zen6 "normale" lo dovrebbe offrire a 128 core, ma 128 core non è possibile ottenerli con 12 chiplet. CCX/CCD X8 = X96. CCX/CCD X12 = X144 CCX/CCD X16 = X192. E va benissimo, in quanto oramai è certo che Zen6 passerà almeno a CCX X12. Quello che non mi torna, è questo: Con Zen6C, AMD passerà dall'N3E di Zen5C all'N3P/N3X di Zen6C, quindi da un PP poco pià denso del liscio (N3E vs N3B) al PP più denso del 2nm (N2P/N2X), incrementando il core cout da X192 a X256 (+33%). Zen6 passerà all'N3P dall'N4P, quindi il salto di densità sarebbe inferiore, eppure aumenterebbe il core count del 50%?

__________________

9950X PBO 1X CO -33 Override +100 CPU-Z RS/DU 930/18.563 - CB23-2339 - 47682 47728 -CB24 144 2508 - OCCT - V-RAY 53.994 - GeekBench 6.3 3563/22664 - TEST RS Y-Cruncher BKT - core 0-15 NPbench - CO -50 + CS -10 (NO RS) CPU-Z-18989 - CB23 48679 - CB24 2593 |

|

|

|

|

|

|

#115 | ||

|

Moderatore

Iscritto dal: Mar 2007

Messaggi: 22646

|

Quote:

Zen5c utilizza i 3nE, ricordo che zen4 C, aveva> 30% di transistor rispetto al zen4 basic. Quote:

I 256 core, saranno presi, con appena 8 CCD, quindi quest'ultimo raddoppierà i core e la cache per CCD, zen 6 basic, aumenterà invece del 50% core e cache. Diciamo che su zen6 basic, è ancora da chiarire la nanometria, ricordo cmq che su zen5 si era sicuri del passaggio ai 3nm, invece hanno sorpreso tutti... L'unica ad averli usati sul desktop è intel, e si sono rivelati imbarazzanti sul suo progetto.

__________________

Ryzen 5800x3D - Msi B450TH - Corsair 32gb 3600 lpx - Red Devil RX 9070XT - samsung 860 pro 1tb - 4tb storage - Acer g-sync xb270hu - AOC CU34G2XPD - MSI MPG A850G atx3.0 |

||

|

|

|

|

|

#116 |

|

Senior Member

Iscritto dal: Jan 2023

Messaggi: 561

|

Appena uscirà un 11960X3D (24 core 3D) ,

considerate il mio 9950X3D in vendita! Speriamo che la mia mobo non dia problemi e che spinga la cpu come deve con il suo PBO .... ... e che il mio Arctic 360 regga!

__________________

9950X3D MSI MAG B850 Tomahawk Max WIFI G.SKILL Trident Z5 6400@cl30

*** Sapphire PULSE 7800 XT su MSI MAG274QRF-QD e LG B4 83" OLED *** Ultima modifica di Xiphactinus : 07-07-2025 alle 08:38. |

|

|

|

|

|

#117 | |||

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 31872

|

Quote:

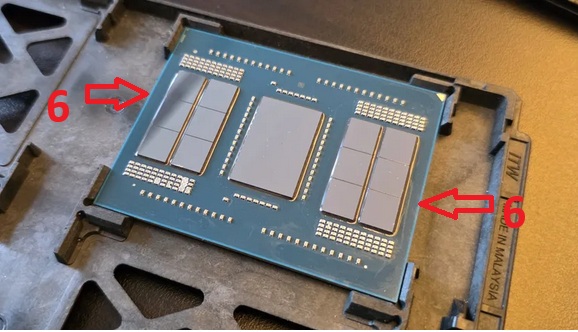

Nelle caratteristiche dal sito AMD non si capisce una tozza perchè non specifica Zen5/Zen5C... ed il socket viene riportato sempre SP5  https://www.amd.com/en/products/proc...05-series.html Io il massimo che ho visto come foto è questo:  Quote:

Cioè, esempio Zen2 aveva 2 CCX X4 per un CCD X8, e questo comportava extra-latenze per il 2° CCX/2a L3. Non ho letto mezza critica sulle latenze di Zen5C, il che mi fa supporre che o l'aumento del core-count sia a livello di CCX o, se più CCX, quantomeno una L3 condivisa tra i CCX. Quote:

Inoltre AMD ha un altro jolly che influisce sui costi finali collegati alla scelta 3nm vs 2nm... l'impilazione della L3, che con Zen6 pare faccia il salto almeno a 2 stradi. Oggi abbiamo il chiplet sull'N4P che nativamente è un X8 + 32MB di L3 di 70mm2 a cui si può aggiungere 64MB di L3 3D a 6nm. Il fatto che si parli di L3 3D non più a 1 livello come ora ma multistrato (quindi come minimo 2 livelli), cambierebbe totalmente i costi di produzione, se implementata per massimizzare. Facendo un esempio di massima, sarebbe come realizzare sempre nei 70mm2 del chiplet N4P, un X16 al posto dell'X8 e impilare totalmente la L3, che avrebbe un PP probabilmente a 4nm e non 3nm o 2nm, tipo 32MB con 1 strato ma anche 96MB con 3 strati. E' palese che in qualsiasi salsa il 2nm costerebbe più del 3nm, ma il costo produzione non ha di per sè un valore massimo, ma si confronta al costo/prestazioni della concorrenza. I 3D AMD è palese che abbiano un costo superiore rispetto ai lisci... ma hanno nel prezzo/prestazioni il loro punto di forza, perchè in primis la maggiorazione del prezzo è di gran lunga superiore all'aumento del costo effettivo e per 2° un benefit gigantesco per AMD nell'appetibilità CPU game. A prescindere dall'offerta core-count specifica per desktop, io sono dell'idea che nel caso di impilazione totale della L3, un Chiplet X16 2nm avrebbe costi non superiori rispetto ad una produzione sul 3nm "tradizionale"... il che vorrebbe dire una corposa diminuzione del costo a core... ed in quest'ottica (che ovviamente al momento indiscutibilmente rimane una mia fantasia

__________________

9950X PBO 1X CO -33 Override +100 CPU-Z RS/DU 930/18.563 - CB23-2339 - 47682 47728 -CB24 144 2508 - OCCT - V-RAY 53.994 - GeekBench 6.3 3563/22664 - TEST RS Y-Cruncher BKT - core 0-15 NPbench - CO -50 + CS -10 (NO RS) CPU-Z-18989 - CB23 48679 - CB24 2593 Ultima modifica di paolo.oliva2 : 07-07-2025 alle 10:17. |

|||

|

|

|

|

|

#118 | |||

|

Moderatore

Iscritto dal: Mar 2007

Messaggi: 22646

|

Quote:

Effettivamente, non sono semplici da ricordare a memoria, ma dalle liste lo si capisce molto bene. Quote:

Zen2 era mediamente simile, 2 CCX da 4 core ma con 4mb l3 per core. Ovviamente, di questo ne avevamo già discusso ampiamente, zen 4 C ha una densità totale >30%, portando la conta transistor per mm2 da 92mt a 121mt. Ora però Zen5 C, usa i core Zen5, che sono anch'essi >30%, di conseguenza quei 121mt, arrivano quasi a 160mt, una roba da 3nm. Quote:

Se guardiamo solo i valori teorici, intel sarebbe dovuta volare, il PP, non è molto diverso dal N3E di zen5c, anzi, paradossalmente ha celle SRAM leggermente meno dense, tuttavia, il boost è passato da 3,1 a 3,7, direi una bella differenza. Intel lato cache 3D, dovrebbe rispondere con la BLLC, mentre per AMD si parla di una 3D a 2 strati, anche se già una porterebbe a ben 144mb, in quanto le griglie cache passeranno dall'8x8 al 8x12. L'uso dei 2nm è possibilissimo pure su zen6, però bisogna vedere realmente quanta densità servirà, ad esempio, zen5 su un 3nm sarebbe stato completamente inutile, visto che la densità media è di 120mt, mentre diventa ben diverso quando devi gestire circa 160mt x mm2 come i core 5C.

__________________

Ryzen 5800x3D - Msi B450TH - Corsair 32gb 3600 lpx - Red Devil RX 9070XT - samsung 860 pro 1tb - 4tb storage - Acer g-sync xb270hu - AOC CU34G2XPD - MSI MPG A850G atx3.0 |

|||

|

|

|

|

|

#119 | |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 31872

|

Secondo me... AMD negli ultimi tempi ha capitalizzato commercialmente la situazione in modo egregio... perchè ha pesato la spesa R&D giusto il minimo per essere competitiva sfruttando le altrui difficoltà, limitando investimentri maggiori R&D architettura/silicio e utilizzo PP silicio top... che avrebbero concesso traguardi ulteriori... io penso sul metro che ad un aumento delle spese non sarebbe seguito un aumento del guadagno proporzionato.

Però la storia ci insegna che quando si capitalizza troppo, il rischio è alto. Io considero un po' rischioso l'utilizzo del 3nm per Zen6 desktop, semplicemente perchè vorrebbe dire stoppare al 3nm anche il mobile, essendo il core Zen6 condiviso, e siccome TSMC ha dichiarato l'1.6nm disponibile commercialmente nel 2028 (ma anche se fosse nel 2029...) non ci sarebbe il tempo fisico per 2 commercializzazioni (intendo esempio 1a uscita Zen6 desktop/mobile 3nm e un refresh sul 2nm) quindi un Zen6 a 3nm desktop/mobile nel 2026 significherebbe che quell'offerta durerà sino al 2028/2029... a me sinceramente pare un po' troppo. Per me è una scelta sbagliata... un bel Nova pimpante X52 sul 2nm a fine 2026 vedrebbe un Zen6 3nm come concorrente per 2 anni... tiferei per Intel Edit. Premetto che essendo un TH di discussione su una CPU futura, penso (e spero) di non essere pesante... Aggiungo. AMD scese in campo con l'MCM semplicemente perchè era VITALE ottenere un prezzo di costo basso, indispensabile per competere con un player che aveva FAB proprie, per pararsi il  da un'eventuale guerra di prezzi. da un'eventuale guerra di prezzi.In tutto ciò AMD è stata anche fortunata, perchè per anni Intel ha fatto 2 sbagli enormi, cioè lottare con AMD nel core-count, con una produzione monolitica vs MCM è palese che abbia ridotto notevolmente i margini e l'avere un PP inferiore ha obbligato scelte al limite (= aumento r&D) nella ricerca della massima prestazione. Ma ora Intel ha il suo MCM, per quanto non sia affinato quanto quello AMD (ovviamente avere 7 anni in più conta), quindi il costo di produzione diventa simile a quello AMD, e la guerra presumibilmente si sposterà su chi riesce ad offrire un costo/prestazioni migliore, perchè è questo che consentirà il maggior volume di vendita. Ed è proprio questo il punto... la soluzione Intel della L3/L4 è comunque una soluzione 2D, che incide sull'area dell'interposer e a cascata sui costi (infatti al momento si parla di integrazione negli Xeon e non è sicuro nel desktop, appunto perchè finchè il processo non è affinato, le rese sono basse e a cascata costi alti, difficilmente applicabile al desktop i cui listini sono ovviamente ben più bassi dei server). Cosa abbiamo di certo lato AMD? In primis l'impilazione della L3 3D sotto al chiplet... di certo ha fatto felice chi si compra un 3D, ma non credo che l'investimento sia finalizzato ai +300MHz di clok finale quanto il fatto che una L3 3D a più strati avrebbe amplificato il problema della dissipazione, ovviamente questo avvalora il fatto che AMD l'impilazione la utilizzerà nei tempi a venire. Io sono dell'idea che il prox passo che potrà fare AMD, sarà quello di rendere MCM il die base (chiplet per AMD e Tile CPU per Intel), con l'intento di produrre sul silicio più costoso solamente l'indispensabile, cioè i core, in quanto la L3 viene comunque prodotta sullo stesso die solamente perchè inserirla esternamente aumenterebbe le latenze per l'esigenza di bus di collegamento, cosa che l'impilazione AMD evita, essendo impilata come fosse lo stesso die. ---------------------------- Quote:

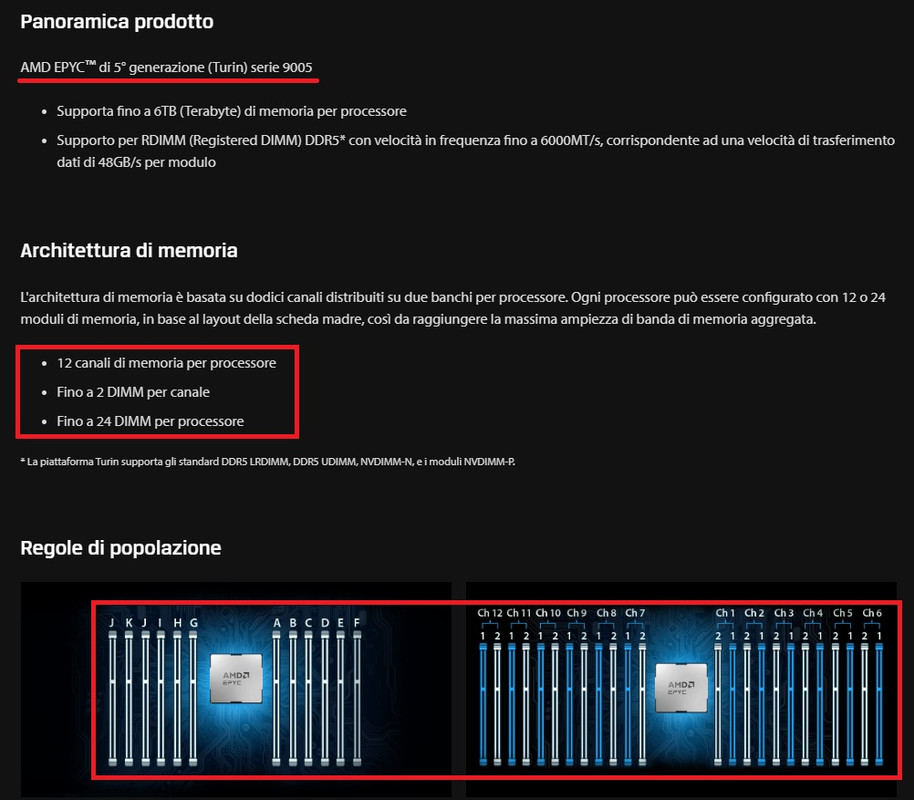

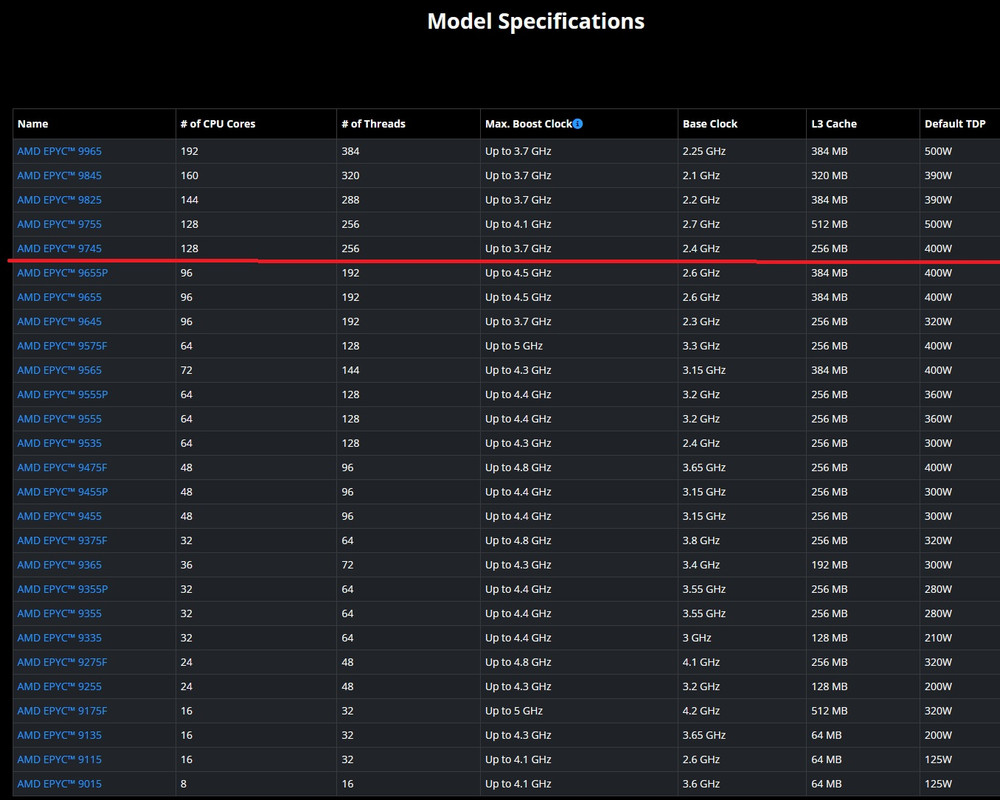

Anche perchè la differenza di clock tra Zen5C e Zen5 è ridicola, -300MHz sulla base e -400MHz sulla massima, ma anche con 400W anzichè 500W di Zen5. Comunque l'implementazione di Zen C nel desktop, se nel rapporto 2:1 (2 core Zen C al posto di 1 "normale") comporterebbe un buon aumento di prestazione ed efficienza. Sono andato a spulciare da AMD "in persona".  Ed effettivamente è come dici tu, Zen5 fino a 128 core, però su massimo 12 canali di DDR. https://ir.amd.com/news-events/press...rn-data-center

__________________

9950X PBO 1X CO -33 Override +100 CPU-Z RS/DU 930/18.563 - CB23-2339 - 47682 47728 -CB24 144 2508 - OCCT - V-RAY 53.994 - GeekBench 6.3 3563/22664 - TEST RS Y-Cruncher BKT - core 0-15 NPbench - CO -50 + CS -10 (NO RS) CPU-Z-18989 - CB23 48679 - CB24 2593 Ultima modifica di paolo.oliva2 : 09-07-2025 alle 07:21. |

|

|

|

|

|

|

#120 |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 31872

|

C'è un link che parlerebbe di Intel Nova vs Zen6 ma è stato rimosso.

Xfastest l'ho già sentito altre volte... è un sito cinese che ha contatti con OEM mobo e quindi riesce a reperire informazioni ad altri sconosciute.  La traduzione del titolo del testo è: "Intel non riesce a tenere il passo con l'architettura AMD Zen 6, deve utilizzare la cache 3D multistrato per migliorare l'IPC e superare Zen 5" C'è da fare una introduzione. A livello di ALU core, AMD non è superiore ad Intel (mi pare che l'IPC Intel sia leggermente superiore), ma AMD, con la L3 3D, riesce ad alimentare meglio i core e questo migliora sia la media dell'IPC che l'efficienza (i loop dei core in attesa dei dati rappresentano una perdita d'efficienza). Non è solamente un discorso di dimensione della L3, ma anche un discorso di latenza... perchè AMD, con l'impilazione, riusce ad aumentare la dimensione della L3 senza variazioni di rilievo delle latenze, mentre soluzioni di aumento L3 al di fuori del die dei core, comporterà comunque un aumento della latenza, ed aumentare la L3 sul die CPU, ne aumenterebbe enormemente i costi.

__________________

9950X PBO 1X CO -33 Override +100 CPU-Z RS/DU 930/18.563 - CB23-2339 - 47682 47728 -CB24 144 2508 - OCCT - V-RAY 53.994 - GeekBench 6.3 3563/22664 - TEST RS Y-Cruncher BKT - core 0-15 NPbench - CO -50 + CS -10 (NO RS) CPU-Z-18989 - CB23 48679 - CB24 2593 Ultima modifica di paolo.oliva2 : 10-07-2025 alle 08:45. |

|

|

|

|

| Strumenti | |

|

|

Tutti gli orari sono GMT +1. Ora sono le: 02:51.