|

|||||||

|

|

|

|

|

|

Strumenti |

|

|

#721 |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4390

|

[QUOTE=Ren

A9 ha 16 stadi non 9. Su k10 e le sue pipe corte con fo4 Bassini, c'è da considerare che quando noi diciamo che un modulo BD è circa uguale ad un un core SB, omettiamo di dire che sono grandi quasi come 2core k10...Il fo4 relativamente piccolo è dovuto anche a questo....Inutile dire che probabilmente una CPU come Nehalem portata a soli 12 stadi avrebbe frequenze ridicole anche sul rinomato finfet di Intel |

|

|

|

|

#722 | |

|

Senior Member

Iscritto dal: Apr 2003

Città: Roma

Messaggi: 3237

|

No, con Twister hanno ridotto la Branch Mispredict Penalty. Adesso sono 9 stadi contro i 16 del cyclone+ (A8)

Probabilmente hanno implementato qualche sistema simile alla loop-cache di intel, ma il salto da 16 a 9 è troppo ampio per esser solo quello. Eccoli il link di anandtech: http://www.anandtech.com/show/9686/t...-plus-review/4 Quote:

Ovviamente la domanda presuppone Consumi diversi, dato che quello più wide assorbirà per forza più watt. Ultima modifica di Ren : 09-03-2016 alle 00:49. |

|

|

|

|

|

#723 | |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4390

|

Quote:

Con BD; AMD avrebbe ridotto solo del 23% il FO4 (+30% di clock a pari vcore) da k10, e al coltempo aumentato il numero degli stadi del 83%... BD e Nehalem, se presi così e venissero semplicemente accorpati alla meno peggio gli stadi farebbero pena lato frequenza (BD avrebbe un FO4 30+ con 11 stadi), idem l'A8. Un'architettura wide, presuppone anche una logica sequenziale piuttosto complessa in grado di sfruttare a dovere le unità disponibili nel ST. Un'ampliamento dell'architettura pressuppone: a) aumento FO4, b) aumento degli stadi (vedi NEHALEM e co), C) riduci la complessità circuitale a scapito del ILP e ti affidi al SMT (vedi IBM) D) hai keller Sul A9, mi pare strano, questo sarebbe un processore COMPLETAMENTE nuovo altro che rivisitazione (cit.) . E a questo si aggiunge un bel boost lato frequenza (+30 e rotti, ma addirittura +72% se consideriamo l'ipad...), D'altra parte ci andrei con i piedi di piombo. Anandtech parla di 9 stadi secchi, e mi pare che sia l'unico a dirlo (se hai altre fonti posta Anche sull'aumento di ipc, ho delle perplessità. Siamo a conoscenza di quanto sia difficile conoscere la reale frequenza di funzionamento nei notebook, ma abbiamo il vantaggio di conoscere l'ipc di una architettura, quindi anche se con difficoltà riusciamo a risalire (una equazione e una incognita). Anandtech né l'uno né l'altro. Ha fatto una stima a ca..o. Io leggo di scaling nel MT COMPLETAMENTE differenti tra ipad e iphone con SoC con la stessa architettura....Tipo scaling del 80% vs 20%....in pratica il confronto è fatto, magari con i software multithread prendendo quella che in realtà è la cosidetta frequenza turbo... Ultima modifica di tuttodigitale : 09-03-2016 alle 10:06. |

|

|

|

|

|

#724 | |

|

Senior Member

Iscritto dal: Apr 2005

Città: Napoli

Messaggi: 6817

|

Quote:

__________________

0 A.D. React OS La vita è troppo bella per rovinarsela per i piccoli problemi quotidiani... IL MIO PROFILO SOUNDCLOUD! |

|

|

|

|

|

#725 |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4390

|

nello specifico mi riferivo ad ipad air 1 vs iphone 5s, entrambi dovrebbero avere lo stesso soc, o sbaglio?

Ultima modifica di tuttodigitale : 09-03-2016 alle 14:23. |

|

|

|

|

#726 | |

|

Senior Member

Iscritto dal: Apr 2003

Città: Roma

Messaggi: 3237

|

Quote:

Sinceramente sembrano competenti(Kanter non è disponibile mi spiace Come hai visto dai bench hanno misurato anche IPC clock-to-clock. (30-40% forse più Che io sappia Apple usa solo il thermal throttle per gli iphone(esistono anche bench sulla solo frequenza). Su Ipad (premium) è molto difficile che riducano considerevolmente il clock per questioni di temperatura (poi dipende dal modello). Ultima modifica di Ren : 09-03-2016 alle 15:18. |

|

|

|

|

|

#727 |

|

Senior Member

Iscritto dal: Apr 2003

Città: Roma

Messaggi: 3237

|

BJT2 che ne pensi di questa storia del Apple A9 (twister) ?

|

|

|

|

|

#728 |

|

Senior Member

Iscritto dal: Dec 2005

Città: Ibiza - Malta - Udine

Messaggi: 6420

|

Scusate, ma non ho seguito e non sono informato...

Mi domando: 1-Quando uscirebbero le prime mobo AM4 e le prime CPU... 2-Ci sarà qualche cosa di compatibile per le "vecchie" mobo FM2+ tramite aggiornamento bios? Visto che la mia Gigabyte riporta un nuovo Bios con il supporto a Carrizzo? Intendo se faranno altre APU compatibili con FM2+ comprendenti pure la parte grafica... cioè NON come l'Athlon X4 845 (che mi pare abbia core Excavator) ??? Possibile che non si sappia nulla...??? Grazie.

__________________

PC: "Che te lo dico a fare" |

|

|

|

|

#729 | ||||

|

Senior Member

Iscritto dal: Nov 2003

Messaggi: 24171

|

Quote:

Quote:

Quote:

Quote:

Zen è previsto entro la fine del 2016 e sarà basato sul socket AM4. Le APU AM4 saranno basate sull'architettura Excavator a 28nm e dovrebbero arrivare prima di Zen. Tutto il resto sono solo rumors...

__________________

AMD Ryzen 9600x|Thermalright Peerless Assassin 120 Mini W|MSI MAG B850M MORTAR WIFI|2x16GB ORICO Raceline Champion 6000MHz CL30|1 M.2 NVMe SK hynix Platinum P41 1TB (OS Win11)|1 M.2 NVMe Lexar EQ790 2TB (Games)|1 M.2 NVMe Silicon Power A60 2TB (Varie)|PowerColor【RX 9060 XT Hellhound Spectral White】16GB|MSI Optix MAG241C [144Hz] + AOC G2260VWQ6 [Freesync Ready]|Enermax Revolution D.F. 650W 80+ gold|Case Antec CX700|Fans By Noctua e Thermalright |

||||

|

|

|

|

#730 |

|

Senior Member

Iscritto dal: Apr 2005

Città: Napoli

Messaggi: 6817

|

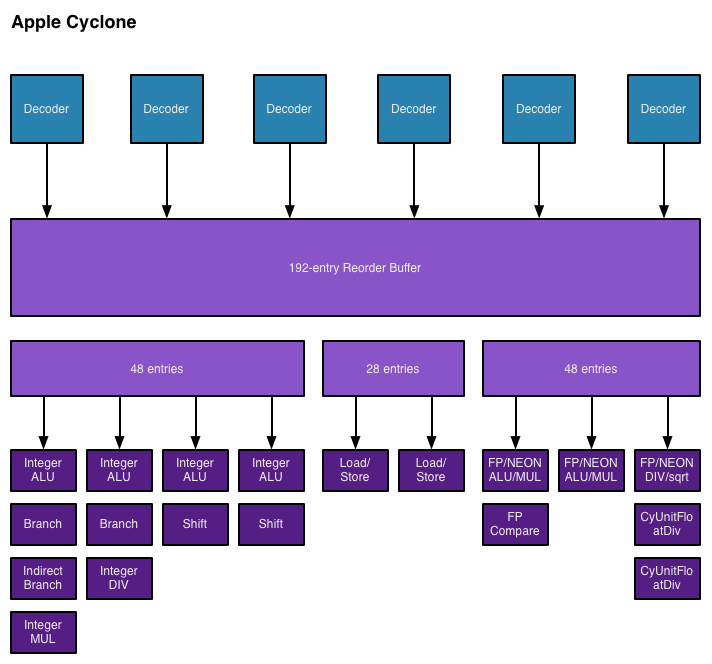

E' un bel processore... E' 6 wide, nel senso che può eseguire 4 alu + 2 mem e poi 3 operazioni fp32 o NEON (SIMD), contro Zen che dovrebbe farne 4, ma ha un IPC fenomenale per chissà quanti accorgimenti a livello di pipeline. Poichè è dato 6 wide issue, deduco che le FP siano in alternativa alle ALU, come INTEL, altrimenti avrebbero detto 9-wide (Zen dovrebbe essere 10-wide), INTEL ha anche clock più che doppi, quindi il paragone non è possibile... Zen potrebbe e dovrebbe avere IPC superiori e per quanto riguarda il clock non c'è storia...

Questo fatto della L3 victim cache porterà svantaggi come per AMD pre-Zen, ma daltronde con una L2 da 3 MB non c'era altro da fare... Ho già scritto i vantaggi di una cache inclusiva... Ma forse poichè i core sono solo due e non 8, il consumo non dovrebbe essere poi così eccessivo...

__________________

0 A.D. React OS La vita è troppo bella per rovinarsela per i piccoli problemi quotidiani... IL MIO PROFILO SOUNDCLOUD! |

|

|

|

|

#731 | |

|

Senior Member

Iscritto dal: Apr 2003

Città: Roma

Messaggi: 3237

|

Quote:

cmq le pipeline fp sono indipendenti come in zen. Twister(A9) può fare 3 mul(128bit).

Ultima modifica di Ren : 09-03-2016 alle 20:38. |

|

|

|

|

|

#732 |

|

Senior Member

Iscritto dal: Feb 2010

Messaggi: 1166

|

Che abbiano effettivamente ridotto la branch misprediction penalty da 16 a 9 cicli di clock può implicare che abbiano accorciato la pipeline, ma questo non significa che l'abbiano portata a 9 stadi.

|

|

|

|

|

#733 | |

|

Senior Member

Iscritto dal: Jan 2002

Città: Urbino (PU)

Messaggi: 32123

|

Quote:

Anche se ci fossero sorprese (negative) sul clock per Zen, Un X8 Zen a 2GHz andrebbe già più di 8370 Questo però è su quanto è trapelato e/o dichiarato da AMD. Però, quello che non mi è chiaro, è che se consideriamo che AMD aveva riportato che le aspettative di clock di Zen si erano già raggiunte con la prima stesura, e si parlava di ALMENO 3GHz di clock def (considerando che AMD quando ha parlato di Zen lo ha sempre riportato X8/95W), direi che addirittura ci sarebbe margine TDP sia per un tiraggio di clock (95W vs 125W/140W) e/o un aumento dei core. Ora... o consideriamo Zen un Opteron (quindi TDP/prestazioni da procio server), vorrebbe dire che se con Piledriver, su un procio desktop di X8 125W AMD ha commercializzato un Opteron raddoppiando i core penalizzando di un 30% la frequenza def (4GHz -30% =2,8GHz), mi sembra plausibile che partendo da 95W (non 125W), Zen con tutta probabilità avrebbe lo stesso raddoppio dei core ma con una diminuzione del clock def in percentuale inferiore... quindi un Zen Opteron X16 è possibile abbia lo stesso clock di un Piledriver X16, cioè circa 2,8GHz, e quindi raddoppio della potenza MT. Personalmente io vedo Zen X8 nativo... probabile X4 APU (mobile), ma non ci vedo un die X6 nativo (commercializzando i fallati però probabile). Non ci vedo logica diversa... con BD, Phenom II (X4/X6) AMD ha sempre optato per una catena con la variante Opteron sempre con la possibilità di 2 die nativi. Realizzare Zen X4/X6 e X8, già vorrebbe dire 3 varianti sulla stessa catena, e se valutassimo la voce di Zen X32 come possibilità di 2 Zen X16 nativi, risulterebbero 4 varianti. Sballerebbero i tempi di quantitativi di commercializzazione, aumenterebbero i costi e si allungherebbero i tempi di affinamento.... Ora come ora, considerando che Carrizo mobile è un X4 e compatibile con il socket AM4, è vero che il salto a Zen X8 sarebbe troppo... ed un Zen X4/X6 troverebbe spazio... ma è anche vero (mia personalissima idea) che l'architettura Zen in accoppiata a tutte le features maturate con Carrizo e trasportate sul 14nm, sulla base di un Zen X8/95W, avrebbe poco senso commercializzare Zen X4 a 45W e Zen X6 a 65W, ma sarebbe più competitivo commercializzare con lo stesso TDP di un 6700K un Zen X8, vuoi sia verso gli X4 Intel che verso i 140W del socket 2011, anche perchè ad un i7 X10/140W, ci sarebbe spazio TDP per un Zen X12 dai 95W di un X8. Comunque rimango dell'opinione, con il mio naso, che non vedo (o credo) in un aumento di forza bruta/core di Zen stile Intel, ma rimango MOLTO ottimista, invece, in un corposo aumento della potenza MT.

__________________

9950X PBO 1X CO -33 Override +100 CPU-Z RS/DU 930/18.563 - CB23-2339 - 47682 47728 -CB24 144 2508 - OCCT - V-RAY 53.994 - GeekBench 6.3 3563/22664 - TEST RS Y-Cruncher BKT - core 0-15 NPbench - CPU-Z 19207 - CB23 49265 - CB24 2593 |

|

|

|

|

|

#734 |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4390

|

x bjt2

sicuro che non ti confondi (mi confondo anch'io non ti preoccupare) wide-issue con il wide instruction execution? (ovvero la cpu in questione sarebbe un 6-wide issue e 9-wide dispatch) Chissà magari anche le ALU di ZEN saranno sulla falsa riga di twister. Ultima modifica di tuttodigitale : 09-03-2016 alle 23:41. Motivo: confusione :) |

|

|

|

|

#735 | |

|

Senior Member

Iscritto dal: Apr 2003

Città: Roma

Messaggi: 3237

|

Quote:

|

|

|

|

|

|

#736 | |

|

Senior Member

Iscritto dal: Apr 2003

Città: Roma

Messaggi: 3237

|

Quote:

ps. cmq anandtech ha davvero troppi dettagli(non dichiarati da apple) per cannare la storia del misspredict... Ultima modifica di Ren : 09-03-2016 alle 23:40. |

|

|

|

|

|

#737 |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4390

|

7 cicli sono comunque enormi, considerano che la fase di decodifica, in una CPU ARM, è marginale rispetto ad una CPU x86..

|

|

|

|

|

#738 |

|

Senior Member

Iscritto dal: Apr 2003

Città: Roma

Messaggi: 3237

|

|

|

|

|

|

#739 |

|

Senior Member

Iscritto dal: Oct 2003

Città: Milano

Messaggi: 4080

|

|

|

|

|

|

#740 |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4390

|

Qui nasce una domanda per bjt2:

Le misure di anandtech sono attendibili? Dice di aver analizzato la penalità media, non avendo informazioni sul numero degli stadi. Ma questa è condizionata enormemente dalle missprediction eventuali nella l1 e l2 (in bulldozer significa perdere altri 20 cicli aggiuntivi). A me pare pure poco 16 medi per typhon. Voglio spiegazioni. Palla a te BJT2. Per me non hanno ridotto le pipeline, se non in misura marginale , rulla a 2,4GHz nel ipad. Ho fatto i calcoli, sono 19mmq per il dual core Cyclone con cache l2, praticamente identico ad un modulo XV con 1MB l2 (entrambi su 28nm e HDL) un dual core typhoon con cache l2, è grande 12,9mmq, che moltiplicato per il maggior fattore di integrazione (2,1x) dei 20nm fa 27mmq.. a maggior ragione twister è una cpu dalla complessità enorme, paragonabile a sandy bridge.... Ultima modifica di tuttodigitale : 10-03-2016 alle 07:02. |

|

|

|

| Strumenti | |

|

|

Tutti gli orari sono GMT +1. Ora sono le: 20:35.