|

|||||||

|

|

|

|

|

|

Strumenti |

|

|

#1 |

|

Member

Iscritto dal: Jun 2006

Città: Salerno

Messaggi: 238

|

FPU con esecuzione fuori ordine

ciao,

Per il mio esame di architetura dei calcolatori mi è stata assegnata la discussione di un paper che tratta un processore in grado di svolgere operazioni in virgola mobile, con la possibilità di eseguire operazioni fuori ordine. Vi linko di seguito il testo integrale del paper dove ho evidenziato le parti relative ai miei seguenti dubbi dubbi: http://www.myupload.dk/showfile/83632de722.pdf 1.è scritto che il processore utilizza "four compliant rounding mode", credo si tratti del parallel rounding algorithm di cui parla a pg 3. Sapete in cosa consiste quest'algoritmo? 2.il coprocessore sotto esame è a 32 bits: s'intende che le istruzioni che tratta (codice operativo + operando) siano lunghe 32 bits o che generi indirizzi di memoria lunghi 32 bits? 3. L'unità aritmetica del coprocessore lavora su valori in virgola mobile a doppia precisione. La differenza tra virgola mobile a precisione doppia/singola è solo nel numero di cifre utilizzate per rappresentare la parte decimale? Per il processore in esame mi pare di capire che i registri del register file hanno 67 bits: 64 per i dati + 3 per gestire le eccezioni , vi pare plausible o ho equivocato?? (nelle architetture studiate nn avevo mai letto di una cosa del genere...) 4.La tecnica della previsione delle eccezioni rende inutile l'uso del reorder buffer: mi spieghereste in parole povere, secondo voi questo come può accadere? grazie, ciao |

|

|

|

|

|

#2 |

|

Member

Iscritto dal: Jun 2006

Città: Salerno

Messaggi: 238

|

up: se nessuno di voi si cimenta , mi deludete....

|

|

|

|

|

|

#3 |

|

Senior Member

Iscritto dal: May 2003

Città: Sperduto nella Franciacorta.

Messaggi: 16377

|

Qua secondo me il 90% delle persona ke passa in questa sezione conosce + o - meno la parte pratica dei processori, io sono uno di quelli, ma ke conosce effettivamnete come funziona il processore qualcuno c'è e ogni tanto salta fuori, ma sono molto pochi.

T'invito a leggere tra i commenti delle prove dei processori ogni tanto salta fuori qualcuno ke se ne intende parecchio.

__________________

Firma da completare ADSL 7M in Italia: http://www.speedtest.net/result/2747466326.png |

|

|

|

|

|

#4 |

|

Member

Iscritto dal: Jun 2006

Città: Salerno

Messaggi: 238

|

ti ringrazio per la diritta, proverò a contattare privamente questi utenti.

ciao |

|

|

|

|

|

#5 |

|

Senior Member

Iscritto dal: Nov 2002

Città: Morbegno (SO)

Messaggi: 1410

|

ricordi eoni fa, ti conviene chiedere in programmazione

__________________

e' difficile cio' che non si conosce Tic Tac Andrew Morton, 15/02/2008 LKML:"`tmp' is an awful identifier, and renaming it to `temp' hardly improves it." |

|

|

|

|

|

#6 |

|

Member

Iscritto dal: Jun 2006

Città: Salerno

Messaggi: 238

|

questa risposta mi è stata data in privato dall'utente Fire Hurricane attualmente sospeso:

2 ) che tratta istruzioni di 32bit, quello della memoria penso sia legato ad una questione di SW. 3) I calcoli in virgola mobile sono svolti dalla FPU (Floating Point Unit) e possono essere di 4 tipi di arrotondamento secondo lo standard IEEE 754: a precisione singola (32 bit) a precisione doppia (64 bit) a precisione singola estesa (≥ 43 bit) a precisione doppia estesa (≥ 79 bit) I calcoli in virgola mobile sono il metodo usato dai processori per elaborazione dei dati e rappresentare numeri razionali (e approssimare numeri reali) in modo simile alla notazione scientifica, però in base 2. Basti sapere questo senza spiegare il campo di mantissa, il campo di esponente e il segno. Purtroppo per spiegare la precisione doppia bisognerebbe spiegare la precisione singola ma hai detto di volere risposte brevi Ricapitolando: la precisione doppia è un metodo di arrotondamento per la visualizzazione di numeri in virgola mobile (utilizzati dalla cpu per compiere operazioni) di lunghezza doppia rispetto a quella singola e pari a 64bit 4) questa non la so di preciso però solo guardando i termini te lo posso spiegare almeno terra terra : il reorder buffer, penso sia un buffer. Sai a cosa serve un buffer no ? funziona come un imbuto trasforma un flusso non continuo in uno continuo e costante senza interruzioni. Una previsioni delle eccezzioni quindi le interruzioni dovute ad applicazioni o ad un segnale SW quindi dovrebbe permettere di saltare all'istruzione successiva in tempo da evitare l'eccezione. 1) BOH ! Sinceramente forse so di che parli ma mi sembra na vaccata. colgo l'occasione per ringraziarlo. |

|

|

|

|

|

#7 | ||||

|

Senior Member

Iscritto dal: Dec 2000

Città: Parma

Messaggi: 3121

|

Prendi tutto con beneficio dell'inventario...non mastico di queste cose da 15 anni.

Quote:

Semplicemente vuole dire che il coprocessore supporta i 4 tipi di 'arrotondamento' previsti dalla ieee754. E' come al solito il problema di rappresentare con una entità continua con un numero che è necessariamente finito. Quote:

1) l'operando è 64 bit, quindi la lunghezza di codice op. + operando è >64bit 2) un coprocessore _non_ ha a che fare con la memoria Semplicemente penso che l'interfaccia fisica con la cpu sia a 32bit Quote:

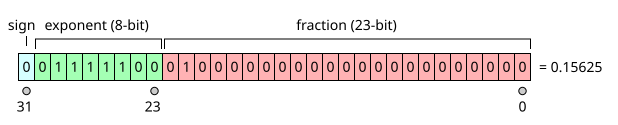

Questo è un fp a doppia precisione:  E questo è uno a singola  Il testo spiega chiaramente che cosa significano i tre bit in più: "the extra three bits stand for that operand is zero, operand in infinite ad operand is NaN" (NAN = Not A Number) E continua: "These bits are set or unset in the last setup of arithmetic computation..." Quote:

Non è un out order sofisticato...in fin dei conti si accontenta di non farti aspettare una radice quadrata quando devi fare delle somme... Immagina di essere un capocantiere e di avere 3 operai. Puoi fare una lista dei lavori che gli devi far fare, ottimizzarla e alla fine passare i compiti ai poveretti o iniziare a dare un compito al primo e poi vedere se il secondo compito è assegnabile ad uno dei rimanenti o se ti tocca aspettare che il primo finisca. In questo secondo caso (che è anche quello del processore) l'inizio delle istruzioni è 'in-order' mentre vengono completate 'out-order'. esempio: sequenza: i1: load 2,2.54 [2 cicli] i2: div 9,10,11 [18 cicli] i3: add 6,7,8 [3 cicli] i4: add 11,2,1 [3 cicli] i5 i6 ... Esecuzione ciclo 1: i1 (blocco registro 2) ciclo 2: i2 (blocco registri 9,10 e 11) ciclo 3: termina i1 (il registro 2 torna disponibile) i3 (blocco registri 6,7 e 8) ciclo 4: i4-----stallo devo accedere al registro 11 bloccato->blocco l'arrivo di nuove istruzioni fino alla risoluzione del problema .... ciclo 6: termina i3 (i registri 6,7 e 8 tornano disponibili) ..... ciclo 20: termina i2 (i registri 9,10 e 11 tornano disponibili) riprendo l'esecuzione di i4 eseguo se possibile i5 Ciao Giovanni |

||||

|

|

|

|

|

#8 |

|

Senior Member

Iscritto dal: Dec 2000

Città: Parma

Messaggi: 3121

|

Dimenticavo...il coprocessore va in stallo (e quindi blocca l'afflusso di istruzioni dalla cpu) anche quando deve eseguire una operazione e la relativa pipeline è occupata.

|

|

|

|

|

| Strumenti | |

|

|

Tutti gli orari sono GMT +1. Ora sono le: 20:36.