Il PCI Express 6.0 corre veloce, siamo già a metà strada

In un mercato dove il PCI Express 4.0 non ha ancora trovato ampia diffusione, il gruppo che si occupa dello standard PCI Express sta correndo veloce per ratificare entro il 2021 il PCI Express 6.0. La nuova specifica ha già raggiunto la versione 0.5.

di Manolo De Agostini pubblicata il 24 Febbraio 2020, alle 18:01 nel canale Schede VideoGeForceRadeonIntelAMDNVIDIA

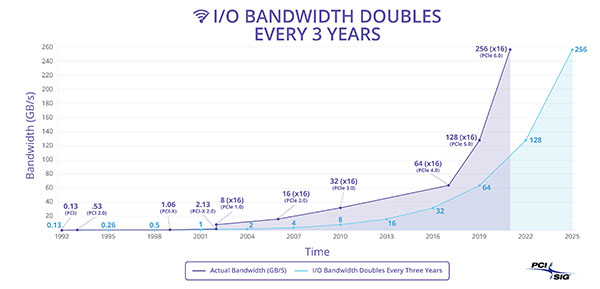

Il PCI-SIG, il consorzio che si occupa dello sviluppo dello standard di interconnessione PCI Express, ha annunciato il raggiungimento della versione 0.5 della specifica del PCI Express 6.0, nuovo standard la cui finalizzazione è prevista per il 2021 e che promette un aumento del bandwidth di otto volte rispetto al PCI Express 3.0, oggi lo standard più diffuso.

Grazie ad AMD e alla sua piattaforma X570 (rimanendo nell'ambito delle piattaforme consumer), la versione commerciale più avanzata del PCI Express disponibile è la 4.0, che garantisce un raddoppio del bandwidth dai 16 GB/s del PCIe 3.0 ai 32 GB/s in configurazione a 16 linee (x16), un passo avanti utile in particolare nell'ambito dell'archiviazione che in quello delle schede video.

Il PCI Express 6.0 vedrà balzare il bandwidth massimo a 128 GB/s (256 GB/s bidirezionali), garantendo maggiori prestazioni in ambito HPC, in quello dell'intelligenza artificiale e del machine learning.

Attualmente Intel non ha ancora piattaforme consumer compatibili con il PCIe 4.0, mentre per quanto concerne il PCIe 5.0 la specifica è completa e formalmente implementabile. Non è chiaro cosa farà AMD nel 2021, quando cambierà piattaforma passando a un nuovo socket (abbandonando il longevo AM4). Lo stesso dicasi per Intel.

Diversa invece la situazione per quanto concerne il settore server, dove la piattaforma AMD EPYC di quarta generazione Genoa basata su architettura Zen 4 dovrebbe supportare il PCIe 5.0, almeno secondo voci di corridoio. La stessa Intel è attesa a un'adozione del PCI Express 5.0 con le soluzioni Xeon note con il nome in codice Sapphire Rapids.

Non bisogna escludere differenze più marcate tra le funzionalità delle piattaforme consumer e server in futuro, anche a fronte della lenta adozione del PCI Express 4.0 e dei requisiti di bandwidth dei rispettivi mercati, con il PCIe 4.0 che potrebbe soddisfare a lungo le necessità dei computer tradizionali.

Quanto al PCI Express 6.0, il completamento della specifica nel 2021 non significa che vedremo prodotti compatibili da subito, ma solo che i produttori di hardware potranno iniziare a sviluppare soluzioni basandosi su una specifica definitiva. L'attuale versione 0.5 è considerata una prima bozza che copre tutti gli aspetti chiave dell'architettura e che contiene i primi feedback dei produttori.

A questo passaggio seguirà la versione 0.7, da considerarsi come una bozza completa, con tutte le specifiche definite e messe alla prova tramite chip di test. A partire da questa versione il PCI-SIG non accetta più l'inclusione di nuove funzionalità. Infine si arriva alla versione 0.9, bozza finale pensata per permettere ai membri del consorzio di analizzare gli ultimi aspetti in vista dell'implementazione. Dopodiché si raggiunge la versione 1.0 e il conseguente rilascio pubblico.

Il PCIe 6.0 rimane retrocompatibile con le precedenti versioni ma vede alcuni cambiamenti per assicurare una maggiore velocità. La differenza più rilevante è il passaggio dalla tecnologia di signaling Non-Return-to-Zero (NRZ) con una codifica tradizionale su due livelli (0 oppure 1) alla Pulse-Amplitude Modulation 4 (PAM4) con quattro livelli di segnali a due bit (00, 01, 10, 11).

Questo consente il trasporto del doppio dei dati senza dover raddoppiare il bandwidth trasmissivo (e di conseguenza la frequenza operativa), ma affinché ciò sia possibile è stato necessario garantire l'integrità del segnale implementando per la prima volta nello standard un meccanismo chiamato Forward Error Correction (FEC). Questa soluzione fa sì che la correzione dei segnali di errore in un collegamento avvenga fornendo un flusso costante di dati per la correzione dell'errore.