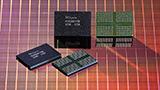

Memoria DDR3: Samsung sviluppa il primo prototipo

Attese al debutto solo nel 2006 le nuove memorie DDR3, capaci di velocitŕ raddoppiate rispetto a quelle DDR2

di Paolo Corsini pubblicata il 18 Febbraio 2005, alle 09:21 nel canale MemorieSamsung

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone'

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone' Appian: non solo low code. La missione è l’ottimizzazione dei processi con l'IA

Appian: non solo low code. La missione è l’ottimizzazione dei processi con l'IA Lenovo ThinkVision 3D 27, la steroscopia senza occhialini

Lenovo ThinkVision 3D 27, la steroscopia senza occhialini  Arriva l'ok da Parlamento europeo sul diritto alla riparazione. Ecco cosa cambierà

Arriva l'ok da Parlamento europeo sul diritto alla riparazione. Ecco cosa cambierà RISC-V: l'uso dell'ISA open-source da parte della Cina preoccupa gli Stati Uniti

RISC-V: l'uso dell'ISA open-source da parte della Cina preoccupa gli Stati Uniti Amazon scatenata: iPad a 399€, airfryer 38€, smartphone, portatili e moltissimi articoli in svendita!

Amazon scatenata: iPad a 399€, airfryer 38€, smartphone, portatili e moltissimi articoli in svendita! SK hynix, costruzione della Fab M15X ai nastri di partenza: previsto boom delle memorie HBM

SK hynix, costruzione della Fab M15X ai nastri di partenza: previsto boom delle memorie HBM Oggi 459€ per utenti Prime il portatile low cost con AMD Ryzen 7 5700U (8C/16T a 4,3GHz), 16GB RAM, SSD 512GB, Full HD!

Oggi 459€ per utenti Prime il portatile low cost con AMD Ryzen 7 5700U (8C/16T a 4,3GHz), 16GB RAM, SSD 512GB, Full HD! Sta per succedere! La prima gara a guida autonoma sarà il 27 aprile: come vederla online

Sta per succedere! La prima gara a guida autonoma sarà il 27 aprile: come vederla online Parthenope: un nuovo RPG investigativo tutto italiano e ambientato a Napoli

Parthenope: un nuovo RPG investigativo tutto italiano e ambientato a Napoli Urbanista Malibu: ecco come va la cassa Bluetooth con ricarica solare

Urbanista Malibu: ecco come va la cassa Bluetooth con ricarica solare Gas Station Simulator è costato 110 mila euro e ha guadagnato più di 10 milioni su Steam

Gas Station Simulator è costato 110 mila euro e ha guadagnato più di 10 milioni su Steam AOC Graphic Pro U3, tre nuovi monitor per i professionisti creativi

AOC Graphic Pro U3, tre nuovi monitor per i professionisti creativi Wacom Movink: per la prima volta il display interattivo ha uno schermo OLED

Wacom Movink: per la prima volta il display interattivo ha uno schermo OLED HPE Aruba presenta i nuovi access point serie 730: oltre il Wi-Fi 7, arriva anche l'IoT

HPE Aruba presenta i nuovi access point serie 730: oltre il Wi-Fi 7, arriva anche l'IoT Lamborghini presenta Urus SE, prima versione ibrida plug-in del Super SUV

Lamborghini presenta Urus SE, prima versione ibrida plug-in del Super SUV

29 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - info15-15-20-38-40T

si... ma un prototipo da 512 non dice nulla.

considerato che nel 2009 512mb saranno nella cache L1

512MB di cache L1 ci saranno forse nel 12009...

Forse tutto questo, come la diffidenza per tecnologie che promettono miracoli, è segno che finalmente gli utenti si svegliano e non danno peso a tutte le sparate delle grand case "finalmente"

...ha capacità di 512 Mbit e opera a 1.5 volt...

se non è un errore di battitura qui si parla di Megabit, non MegaByte... inoltre si parla di componente, non di banco completo, per come ho inteso io dovrebbe trattarsi del singolo chip di memoria, e un chip da 64MB non mi sembra così piccolo...la latenza di questo sample quant'è?

15-15-20-38-40T

Le latenze non sono importanti per le schede video...

le dd3 per memorie video esistono già

Re: ...ha capacità di 512 Mbit e opera a 1.5 volt...

se non è un errore di battitura qui si parla di Megabit, non MegaByte... inoltre si parla di componente, non di banco completo, per come ho inteso io dovrebbe trattarsi del singolo chip di memoria, e un chip da 64MB non mi sembra così piccolo...

appunto... il piccolo dettaglio è che quel componente, all' atto pratico verrà impiegato quasi sicuramente assieme a 7 esemplari uguali... per formare un banco da 512 MByte

sulle rambus, io sono ancora convinto che, soprattutto per l'epoca in cui uscirono, siano una tecnologia dal valore non indifferente, ... obiettivamente:

canali a 800-1200 mhz, a 16 bit ognuno , ma aggregabili fino a 4 od 8 come adesso si fa col pci express

una 30ina di piste per canale, invece delle 200 che servono per un singolo ddr channel a 64 bit

protocollo di comunicazione: i segnali di indirizzamento di righe e colonne vengono mandati assieme, seguiti da un unico segnale di STrobe (convalida) (piuttosto che Colonna- e poi STrobe, Riga - e poi di nuovo STrobe), per poi riutilizzare le piste per i dati in arrivo/uscita: in questo modo il valore scritto sui moduli (45 ns sui primi , su quelli successivi si arriva a 30) corrisponde alla latenza totale di transito attraverso il modulo (trattandosi appunto di CANALE e non di un BUS, i segnali devono propagarsi, e attraversare tutti i device che sul canale si trovano)

il problema delle rambus stava essenzialmente nel prezzo dei moduli in confronto alle DDR , nelle royalties, e nel fatto che, data la costruzione dei moduli di qualche anno fa, mettendone assieme più di uno per canale (cosa più che probabile sui server e le workstation), le latenze di attraversavento si sommano, e si passa da valori in nanosecondi tutto sommato paragonabili al totale di un canale DDR CAS3, si arriva a uno svantaggio che si avverte di più in ambiti in cui gli accessi in ram siano "sparsi" (DB...)

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".