TSMC, ci sono i 3 nanometri nel futuro della Fab in Arizona: una buona notizia per Apple?

A pochi giorni dalle voci di una Apple intenzionata a spostare parte della produzione dall'Asia ad altre regioni per non rendersi troppo dipendente da un'unica area geografica, arrivano le parole del fondatore di TSMC sui piani in Arizona: i 3 nanometri, utile ad Apple, sarebbero gi‡ nel mirino.

di Manolo De Agostini pubblicata il 21 Novembre 2022, alle 10:01 nel canale AppleAppleTSMC

Nei giorni scorsi si è discusso dell'intenzione di Apple di smarcarsi dalla produzione asiatica per approvvigionarsi di chip realizzati negli Stati Uniti o in Europa. In particolare, i riflettori si sono puntati su TSMC e la sua fabbrica in Arizona, attualmente in costruzione.

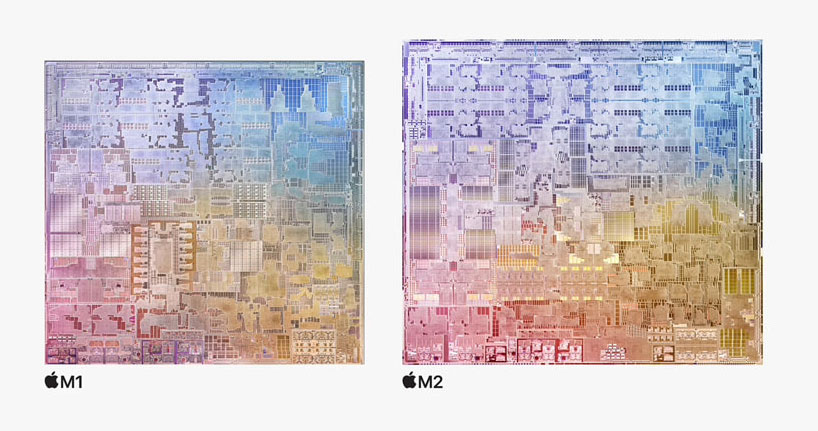

Il rapporto tra Apple e TSMC, infatti, è molto solido e definito, quindi il prosieguo della collaborazione seppur negli Stati Uniti risulta la strada più sensata. Poiché in Arizona la fonderia taiwanese prevede di produrre inizialmente con processo a 5 nanometri, tecnologia che seppur avanzata non rappresenta la sua punta di diamante, si è vociferato di un possibile cambio dei piani per andare incontro ai desiderata di Apple.

Ed è di questo argomento (seppur mai citando Apple), come riporta Reuters, che ha parlato il fondatore del colosso taiwanese Morris Chang. "Tre nanometri, TSMC ha un piano in questo momento, ma non è stato completamente finalizzato. È stato quasi completato - nello stesso sito dell'Arizona, come fase due. I 5 nanometri sono la fase uno, i 3 nanometri la fase due".

Il processo a 3 nanometri (N3) di TSMC promette di offrire un miglioramento della densità logica fino al 70% rispetto all'N5, con un miglioramento prestazionale fino al 15% a parità di consumo o fino al 30% di consumo in meno alla stessa velocità.

Benché Chang non sia più nella società taiwanese, rimane molto influente e con una visione d'insieme sui piani di TSMC. Proprio quest'ultima terrà una cerimonia in Arizona il 6 dicembre per segnare un passaggio importante della costruzione dell'impianto, il cosiddetto "tool in". Per l'occasione sarà presente il Segretario per il Commercio Gina Raimondo, e non è esclusa la partecipazione del Presidente USA Biden. Forse in quel momento TSMC farà completamente luce sulle sue intenzioni.

"Ci sono molte persone gelose, gelose dell'eccellente produzione di chip di Taiwan", ha detto Chang commentando i piani di Stati Uniti ed Europa per spingere la produzione locale di microchip. "Quindi ci sono anche molte persone che per vari motivi, sia per la sicurezza nazionale che per fare soldi, sperano di produrre più chip nei loro paesi. Molti paesi mi hanno chiesto se possiamo produrre chip da loro", ha concluso l'imprenditore senza però entrare nel dettaglio.

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone'

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone' Appian: non solo low code. La missione è líottimizzazione dei processi con l'IA

Appian: non solo low code. La missione è líottimizzazione dei processi con l'IA Lenovo ThinkVision 3D 27, la steroscopia senza occhialini

Lenovo ThinkVision 3D 27, la steroscopia senza occhialini  Sta per succedere! La prima gara a guida autonoma sarà il 27 aprile: come vederla online

Sta per succedere! La prima gara a guida autonoma sarà il 27 aprile: come vederla online Parthenope: un nuovo RPG investigativo tutto italiano e ambientato a Napoli

Parthenope: un nuovo RPG investigativo tutto italiano e ambientato a Napoli Urbanista Malibu: ecco come va la cassa Bluetooth con ricarica solare

Urbanista Malibu: ecco come va la cassa Bluetooth con ricarica solare Gas Station Simulator è costato 110 mila euro e ha guadagnato più di 10 milioni su Steam

Gas Station Simulator è costato 110 mila euro e ha guadagnato più di 10 milioni su Steam AOC Graphic Pro U3, tre nuovi monitor per i professionisti creativi

AOC Graphic Pro U3, tre nuovi monitor per i professionisti creativi Wacom Movink: per la prima volta il display interattivo ha uno schermo OLED

Wacom Movink: per la prima volta il display interattivo ha uno schermo OLED HPE Aruba presenta i nuovi access point serie 730: oltre il Wi-Fi 7, arriva anche l'IoT

HPE Aruba presenta i nuovi access point serie 730: oltre il Wi-Fi 7, arriva anche l'IoT Lamborghini presenta Urus SE, prima versione ibrida plug-in del Super SUV

Lamborghini presenta Urus SE, prima versione ibrida plug-in del Super SUV Scuderia Ferrari e HP insieme: ufficiale il nuovo accordo per la Formula 1

Scuderia Ferrari e HP insieme: ufficiale il nuovo accordo per la Formula 1 Snapdragon X Plus, un nuovo SoC per i notebook Windows

Snapdragon X Plus, un nuovo SoC per i notebook Windows L'iPad 10,9'' 64 GB Ë sceso a meno di 400 euro. E occhio anche al modello con 256 GB

L'iPad 10,9'' 64 GB Ë sceso a meno di 400 euro. E occhio anche al modello con 256 GB Steam: basta ai furbetti dell'accesso anticipato, niente rimborsi dopo due ore di gioco in ogni caso

Steam: basta ai furbetti dell'accesso anticipato, niente rimborsi dopo due ore di gioco in ogni caso Motorola Edge 40 Neo con fotocamera da 50 MP OIS e display OLED a 291 euro su Amazon. E occhio alle altre offerte Motorola

Motorola Edge 40 Neo con fotocamera da 50 MP OIS e display OLED a 291 euro su Amazon. E occhio alle altre offerte Motorola Arriva Kasperksy Next, la nuova gamma di soluzioni di sicurezza per le imprese

Arriva Kasperksy Next, la nuova gamma di soluzioni di sicurezza per le imprese

6 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoLe "misure in nanometri" non sono reali, vanno interpretate come "se questo chip fosse realizzato con gate mosfet lineari, dovrebbe avere questa feature size in nanometri per avere la stessa densità del nostro processo produttivo".

Quindi se non entrano in gioco nuovi materiali, o dopo finfet e ribbonfet, ecc. si inventano una nuova geometria del gate, oppure inizieranno a puntare sempre più sullo stacking dei chip e sul migliorare le interconnessioni tra più stack di chiplet, ecc. ecc.

Ci sono già potenziali sostituti del silicio, ma sebbene molto interessanti non si riesce a produrre wafer altrettanto grandi e con pochi difetti come invece avviene da decenni col silicio.

Per esempio, recentemente si sono fatti grandi progressi col carburo di silicio (SiC), ma é ancora molto lontano dal poter essere usato costruire circuiti integrati complessi (fortunatamente si continua ad investire sull'elettronica SiC perché ha un sacco di utilizzi nell'elettronica di potenza o per roba che deve funzionare ad alte temperature o in presenza di radiazioni forti).

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".