|

|||||||

|

|

|

|

|

|

Strumenti |

|

|

#21 | |

|

Senior Member

Iscritto dal: Mar 2016

Messaggi: 2061

|

Quote:

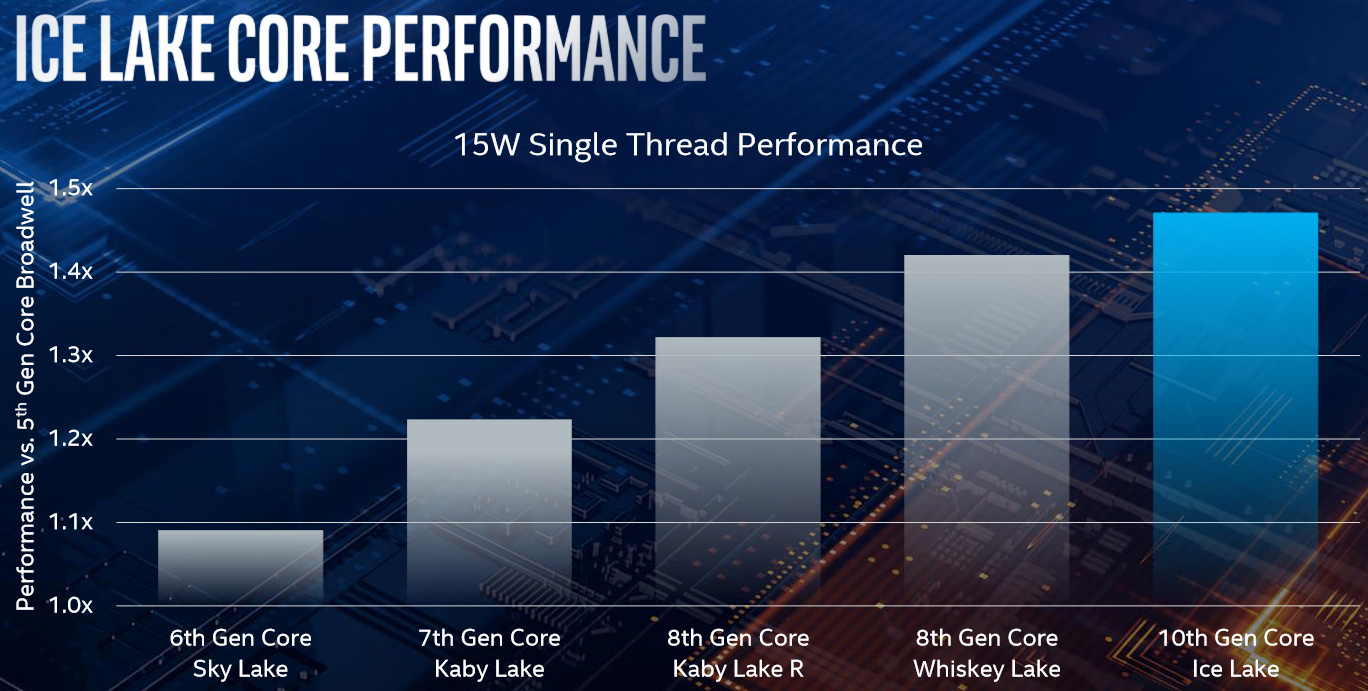

dal grafico si passerebbe da un 1.42% di whiskey lake ad un 1.48% di ice lake, ho completato la seconda cifra decimale a spanne da quanto si evince dalla slide...vorrei capire anche io da dove arriva tale dato...

__________________

fanboy del mio portafoglio... |

|

|

|

|

|

|

#22 |

|

Senior Member

Iscritto dal: Oct 2001

Messaggi: 14720

|

@cdimauro

Credo che il dato sia sbagliato, perchè per la tabella sottostante dice chiaramente che si tratta di un incremento di prestazioni single thread dovuto non solo all'IPC, ma anche agli aumenti di frequenza a parità di consumo. Inoltre se prendiamo i valori in tabella l'incremento tra Wiskey Lake e Ice Kale passa spannometricamente da 1,42x a 1,47x. Se Wiskey Lake è uno, Ice Lake diventa circa un 3,5% di incremento. E non un incremento di IPC. Insomma, in quei valori potrebbero essersi dimenticati una virgola (da 1,5% a 1,8%) se si parla esclusivamente i IPC (anche se ad occhio direi che dovrebbero essere un po' più alti). |

|

|

|

|

|

#23 |

|

Junior Member

Iscritto dal: Jan 2001

Messaggi: 96

|

no 10nm no party, ma le tecnologie sembrano fighe

|

|

|

|

|

|

#24 | |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4078

|

Quote:

ma nel grafico i miglioramenti delle prestazioni nel ST sono intorno al 4% rispetto all'8a generazione... le possibilità sono 2: 1) clock massimo decisamente più basso. 2) scaling del Hyperthreading migliorato. un "piccolo" indizio c'è.... il clock turbo passa dai 4,8GHz Core i7-8665U (TDP 15W) ad un tutt'altro assicurante fino a 4,1GHz (e TDP fino a 28Watt)... e il fatto che il confronto Intel l'abbia limitato agli sku fino a 15W (con un miglioramento minimo) la dice lunga quanto i 14nm siano superiori ad alte frequenze.... Ultima modifica di tuttodigitale : 29-05-2019 alle 14:59. |

|

|

|

|

|

|

#25 |

|

Senior Member

Iscritto dal: Mar 2016

Messaggi: 2061

|

ma skylake è del 2015...

__________________

fanboy del mio portafoglio... |

|

|

|

|

|

#26 |

|

Senior Member

Iscritto dal: Sep 2010

Messaggi: 4078

|

l'ipc è identico, Intel dal 2016 propone la solita architettura. Quello che è successo negli ultimi è stato un aumento della frequenza di clock e il numero di core.

Ultima modifica di tuttodigitale : 29-05-2019 alle 15:03. |

|

|

|

|

|

#27 |

|

Senior Member

Iscritto dal: May 2004

Messaggi: 6519

|

|

|

|

|

|

|

#28 | |

|

Senior Member

Iscritto dal: Oct 2001

Messaggi: 14720

|

Quote:

E anche se si parlasse di SkyLake, mi sembra comunque esagerato, a meno che non ci siano grossissime problematiche sul salire di frequenza persino con questi TDP. |

|

|

|

|

|

|

#29 | |

|

Senior Member

Iscritto dal: Oct 2003

Città: Milano

Messaggi: 4053

|

Quote:

__________________

spesso, è solo quando sai che non ti resta molto tempo che ne apprezzi il reale valore quote: "some users are a classic example of the inverse ratio between the size of the mouth and the size of the brain" * se non vi rispondo è perché siete (200+) nella mia ignore list * mi chiedo perché chi è nella ignore list è spesso sospeso e, prima o poi, viene bannato * |

|

|

|

|

|

|

#30 |

|

Senior Member

Iscritto dal: Oct 2001

Messaggi: 14720

|

Mi sembra però inverosimile che la soglia del clock "turbo" possa incidere tanto sulle prestazioni, dato che su processori con questi TDP quelle frequenze possono essere utilizzate solo per brevi periodi di tempo.

|

|

|

|

|

|

#31 |

|

Senior Member

Iscritto dal: Mar 2016

Messaggi: 2061

|

con tutte le variabili sul tavolo non si puo' che attendere una prova reale sul campo per determinare la validità di questo prodotto. Dalle slide e dalle informazioni snocciolate mi sembra che si possa dire tutto e il suo contrario...

__________________

fanboy del mio portafoglio... |

|

|

|

|

|

#32 | ||||

|

Senior Member

Iscritto dal: Jan 2002

Città: Germania

Messaggi: 26107

|

Quote:

Quote:

Per il resto, concordo con quanto scritto qui sotto. Quote:

Quote:

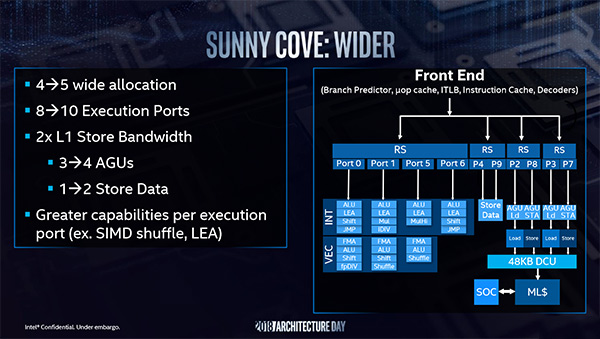

nella porta 0 l'unità vettoriale è in grado di eseguire FMA, ALU, o Shift a 512-bit, mentre nella porta 5 può eseguire ALU o Shuffle a 512-bit. Dunque per le operazioni più comuni è in grado di eseguire 2 operazioni a 512-bit alla volta. Che non è poco, sia chiaro, anche perché le AVX-512 consentono di eseguire più "lavoro utile" per istruzione eseguita (rispetto alle AVX c'è la possibilità di eseguire nativamente il masking o l'azzeramento delle "linee" dati, il broadcasting oppure l'arrotondamento o soppressione degli errori), e inoltre c'è il notevole vantaggio di lasciare libere le altre porte per le normali operazioni intere/"scalari".

__________________

Per iniziare a programmare c'è solo Python con questo o quest'altro (più avanzato) libro @LinkedIn Non parlo in alcun modo a nome dell'azienda per la quale lavoro Ho poco tempo per frequentare il forum; eventualmente, contattatemi in PVT o nel mio sito. Fanboys |

||||

|

|

|

|

|

#33 |

|

Amministratore

Iscritto dal: Jul 1999

Città: Luino

Messaggi: 4837

|

Saluti a tutti: sono a Taipei per il Computex e il tempo è sempre troppo poco in questi casi. A quanto mi risulta, ma cercherò di riverificare ulteriormente per scrupolo, Sunny Cove implementa le motigations per Spectre e Meltdown.

Circa l'incremento prestazionale tra 15% e 18% è un dato emerso durante la sessione tecnica sull'architettura Sunny Cove alla quale ho partecipato nelle scorse settimane; per Intel è un incremento medio ottenuto con un pacchetto di applicazioni (non meglio specificate al momento).

__________________

"I decided to go for a little run." - Follow me on Strava |

|

|

|

|

|

#34 |

|

Senior Member

Iscritto dal: Jan 2002

Città: Germania

Messaggi: 26107

|

Sessione tecnica -> è molto probabile che il 15-18% di miglioramento sia dovuto proprio all'IPC. Direi ottimo se fosse confermato, e d'altra parte la nuova micro-architettura presenta delle notevoli migliorie per cui sarebbe anche in linea con le aspettative.

Riguardo alle falle di sicurezza, già con Cascade Lake buona parte delle mitigazioni sono hardware (quindi senza perdite prestazionali), come riportato dalla documentazione di Intel e da un articolo di AnandTech dello scorso anno. Come si può vedere da quest'ultimo link, dopo Cascade Lake arriverà (quest'anno) Cooper Lake e poi Ice Lake. Quindi è probabile che arriveranno ulteriori mitigazioni hardware con questi ultimi.

__________________

Per iniziare a programmare c'è solo Python con questo o quest'altro (più avanzato) libro @LinkedIn Non parlo in alcun modo a nome dell'azienda per la quale lavoro Ho poco tempo per frequentare il forum; eventualmente, contattatemi in PVT o nel mio sito. Fanboys |

|

|

|

|

|

#35 | |

|

Senior Member

Iscritto dal: May 2004

Messaggi: 6519

|

Quote:

Mentre nella porta 5 può eseguire ALU o Shuffle a 512-bit questo si ma è comunque limitata rispetto alla porta 5 delle cpu xeon odierne che invece hanno un unita a 512bit completa. Ultima modifica di coschizza : 30-05-2019 alle 08:03. |

|

|

|

|

|

|

#36 |

|

Senior Member

Iscritto dal: Jan 2002

Città: Germania

Messaggi: 26107

|

Allora c'è un errore nel grafico, perché si vede chiaramente che la porta 1 non abbia alcun legame con AVX-512.

Francamente un errore del genere da parte di Intel, in una presentazione ufficiale strombazzata ai quattro venti, mi pare leggermente difficile. A mio avviso il diagramma è corretto. D'altra parte questa non è la prima implementazione di AVX-512, per cui ci può anche stare che la soluzione micro-architetturale sia diversa da quelle precedentemente implementate. Visto che Paolo è da quelle parti, potrebbe chiedere delucidazioni anche su quest'informazione. IMO ne verrebbe fuori una notizia interessante per HWU, visto che sarebbe la prima a pubblicare un dettaglio non di poco conto che sembra sia sfuggito ad altri.

__________________

Per iniziare a programmare c'è solo Python con questo o quest'altro (più avanzato) libro @LinkedIn Non parlo in alcun modo a nome dell'azienda per la quale lavoro Ho poco tempo per frequentare il forum; eventualmente, contattatemi in PVT o nel mio sito. Fanboys |

|

|

|

|

|

#37 | |

|

Senior Member

Iscritto dal: May 2004

Messaggi: 6519

|

Quote:

Ultima modifica di coschizza : 30-05-2019 alle 08:23. |

|

|

|

|

|

|

#38 |

|

Senior Member

Iscritto dal: Jan 2002

Città: Germania

Messaggi: 26107

|

Sì, ho appena ricontrollato, ed è così. Ma l'avevo scritto anche prima: probabilmente questa è la sola versione mobile. Per desktop e server (almeno su questo sicuramente) mi aspetto quella della precedente presentazione.

__________________

Per iniziare a programmare c'è solo Python con questo o quest'altro (più avanzato) libro @LinkedIn Non parlo in alcun modo a nome dell'azienda per la quale lavoro Ho poco tempo per frequentare il forum; eventualmente, contattatemi in PVT o nel mio sito. Fanboys |

|

|

|

|

|

#39 |

|

Senior Member

Iscritto dal: Jan 2002

Città: Germania

Messaggi: 26107

|

Meglio mettere la slide in questione:

Allora luce di quanto discusso e delle differenze fra le due slide, sono ragionevolmente sicuro che Ice Lake mobile NON combini le porte 0 e 1 per calcolare le AVX-512. Quindi la porta 0 è già di per sé a 512 bit, e totalmente indipendente dalla porta 1. Questo, se ci pensiamo bene, ha molto senso: Ice Lake versione desktop/server è il design completo (con ben 3 porte a 512-bit: 0, 1, e 2), mentre quella mobile qui presentata è la versione "castrata". Peraltro scelte simili potrebbero anche essere fatte per le versioni desktop (quindi lasciando a quelle server l'implementazione più performante). Ad esempio Intel potrebbe replicare la porta 0 e la porta 1 (quindi 2 FMA), lasciando la 5 come la versione mobile. Oppure replicare la porta 5 e la 1 (quindi ancora 1 sola FMA). La prima soluzione la troverei più papabile, visto che le versioni desktop hanno un power budget ben più elevato di quelle mobile, e inoltre Intel ha bisogno di mostrare di poter macinare più numeri.

__________________

Per iniziare a programmare c'è solo Python con questo o quest'altro (più avanzato) libro @LinkedIn Non parlo in alcun modo a nome dell'azienda per la quale lavoro Ho poco tempo per frequentare il forum; eventualmente, contattatemi in PVT o nel mio sito. Fanboys |

|

|

|

|

|

#40 | |

|

Senior Member

Iscritto dal: Oct 2001

Messaggi: 14720

|

Quote:

Forse il pacchetto software Intel citato da Paolo Corsini include software che sfrutta le AVX-512, dove potrebbe risiedere gran parte del guadagno. Oppure viste le difficoltà a salire con i 10nm con questa microarchitettura hanno deciso di penalizzare le frequenze e puntare tutto sull'IPC per compensare, del resto hanno aggiunto un bel po' di unità di calcolo. |

|

|

|

|

|

| Strumenti | |

|

|

Tutti gli orari sono GMT +1. Ora sono le: 12:07.

_L.jpg)

_XXL.jpg)