Quote:

Originariamente inviato da paolo.oliva2

Non ti seguo... Zen2 aveva CCX da X4, è Zen3 cha passa il CCX a X8... e tutti i CCX mobile sono X8 con 16MB di L3, ma non c'è nessun crollo prestazionale... (nel mobile) anzi, AMD da' l'IPC di Zen4C uguale a Zen4 e fino a -3% nel caso di programmi fortemente L3 dipendenti.

Cioè... con Zen2 avevamo 2 CCX X4 ciascuno con 16MB di L3, e con Zen3 si passa a CCX X8 con 32MB di L3, la L3 a core è la stessa ma si elimina la latenza di collegamento tra le 2 L3 (16MB CCX1 e 16MB del CCX 2).

Ma non è una esclusiva del core C, nel senso che i 2MB o 4MB di L3 a core li vediamo anche nei core non C, ad esempio nel mobile, ma mi pare anche nel desktop su alcuni modelli.

|

La l3 come sempre detto, non è a core, ma globale. Zen2 era a CCX da 4x16, ma la latenza per core era oltre il doppio. Che voresti tornare al sistema dei 3000? Va bene per applicazioni di calcolo non certo per prestazioni come giochi, compressioni etc.

Con zen6 si dovrebbe svoltare sulle latenze tra CCD, e vogliamo tornare ai CCX.

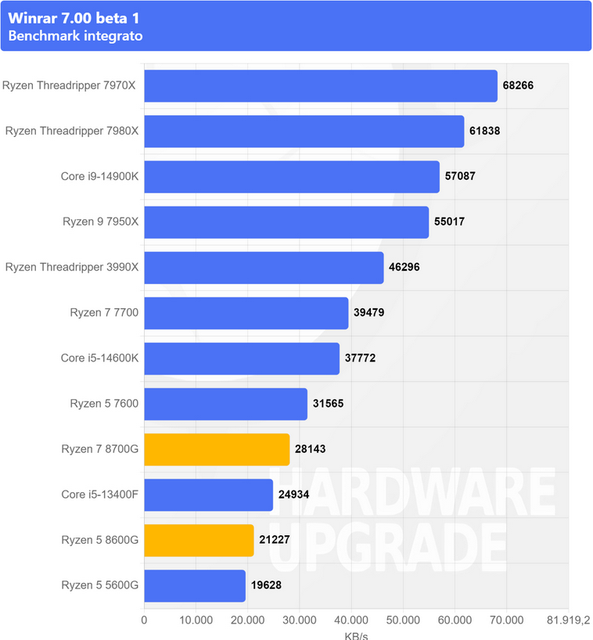

Riguardo il 8700g, grazie alla struttura CCD, mantiene tutti rapporti core to core ed IPC di zen4, ma dove serve la cache, sbanda terribilmente, vedi giochi e compressioni.

Chiaro, va bene nel calcolo, come anche un CB, ma li pure con 96mb di cache non guadagni.

Quote:

Originariamente inviato da paolo.oliva2

Le perdite che si vedono tra L3 da 2MB/core e 4MB/core non riflettono la realtà... perchè sono L3 da 32MB per 8 core con latenza mi pare 40, dimezzate a 16MB come capacità ma sempre con la medesima latenza dei 32MB.

Cioè, se si fa il test delle cache/DDR con AIDA, la L1/L2/L3 viaggiano tutte ad una frequenza simile a quella dei core, ma la banda è data dalla latenza e la latenza è in base alla dimensione della cache.

Che 16MB di L3 per 8 core riportino una incidenza maggiore di cache missing rispetto a 32MB, è certo... però questo lo si valuta con la predizione Zen4, con una frequenza/latenza L3 riferita al 5nm, con DDR5 a 6000, con una frequenza di 2GHz per l'NB, con latenza 40...

Una predizione migliore, una latenza di 20 per 16MB anzichè 40 per 32MB, una frequenza NB non limitata a 2GHz ma a 5GHz, delle DDR5 non 4800/6000 ma 10K/12K, una L3 a frequenza più alta... e non dimentichiamoci la L3 3D.

|

I test di Aida non fanno altro che fare il calcolo clock x bus cache e latenza ram, quindi effettuano il rappoto cicli ghz/ns.

Se tu avessi 10ghz, anzichè 5, avresti 2x la banda l1/l2/l3. Quella non viene tagliata.

Con le ram più veloci, tramite ghz/latenza avrai valori migliori, ma questo è un'altra cosa.

Quote:

Originariamente inviato da paolo.oliva2

Perdonami ma non riesco a comprendere il filo... AMD dovrebbe aspettare nanometrie più dense per l'ibrido, mentre Intel è ricorsa all'ibrido proprio per la mancanza di nanometrie più dense... cioè, Intel ha fatto l'ibrido su Intel7 che è una nanometria meno densa del 7nm TSMC... mentre per AMD parliamo del 4nm che è un'enormità più denso e dovrebbe aspettare cosa? Il 2nm?

Poi c'è un discorso tutto differente di implementazione ibrida tra AMD ed Intel... che è difficile da spiegare.

AMD inserisce 1 core C al posto di 1 core P, per rendere più efficiente l'aumento di prestazione, perchè in fin dei conti il core C è un core ottimizzato e più denso per operare a frequenze leggermente inferiori, con lo stesso ISA, stesso IPC e sempre SMT2, e virtualmente il funzionamento ottimale lo avrebbe in MT con carico 100% dove la differenza di frequenza è minima in quanto i core P hanno frequenze ben inferiori a quella turbo massima, e di qui la differenza con i core C è ovviamente inferiore.

Intel inserisce 2 core E al posto di 1 core P, ma i 2 core E non uguagliano la prestazione del core P, perchè non sono SMT2 e perchè hanno un IPC inferiore... a cui si aggiunge il prb ISA diverso. Quanto core E servono per uguagliare la prestazione di 1 core P? 3? 4? In AMD già 2 core C supererebbero nettamente il core P. Io non conosco le aree precise Intel... ma mi pare di ricordare che il core P Intel è più grasso del core Zen4 (tra densità e numero transistor), e non credo che 1 core Zen4C occupi un'area maggiore rispetto a 3-4 core C Intel... non ho i dati precisi, ma mi pare che il core Zen C vinca su tutto sul core E Intel, prestazione/area e prestazione/consumo.

|

Certo, la densità è importantissima, ed il problema appunto, è la cache l3.

Come vedi sui 32 core, raddopierà pure la l3 che è oltre 1/3 di die.

Intel infatti, per collegare gli e core, gli ha aumentato la l3, ed ha dovuto bombardare di l2 (che è molto più grossa della l3) per evitare che gli ecore si mangiassero la loro l2 e saturassero buona parte di l3.

I p-core, se non avesso gli e core, avrebbero 24mb di l3 e 16mb di l2.

Con gli e core, passano a 36mb di l3 e ben 32mb. Di fatto raddoppiano la l2 e 1,5 la l3.

Come vedi, per mantenere quei core extra, devono bombardare di cache, non a caso raptor è una padella da quasi 260mm2, roba da rtx 4070ti quasi.

Inoltre gli e core non sono come i core dense, sono stati proprio una pezza, in quanto era inconcebile mettere 16 p core, altrimenti non ricorevvi a questo.

Lo sai che la latenza ibrida core to core è equivalente a quella di zen2?

L'ibrido volendo potresti pure farlo su AMD, tramite un CCD basic ed uno Dense, oppure, non potendo dividere in 2 CCX, colleghi un 8+16 ad una cache molto più grande, ed ecco che ti serve densità.

Il calcolo che fai tu, è trovare un modo per avere performance brute, sacrificando l'IPC e il ST a scappito del puro MT.

Quote:

Originariamente inviato da paolo.oliva2

Presumo che intendi 16 core a CCX per 32 core totali.

L'8.8 GT/S... abbiamo superato già i 10 GT/s (anche se in OC).

https://www.hdblog.it/hardware/artic...mhz-overclock/

A mio parere non li vedremo più 32 core P sul desktop... perchè tra aumento iGPU e implementazione IA...

Ma è proprio per l'IA che io presumerei un aumento del core-count ma su core C... perchè (mia impressione e posso sbagliarmi) l'IA predilige un numero superiore di logiche meno potenti rispetto a meno logiche più potenti. |

No, il CCX sui core basic non ci interessa, si intende CCD, quindi jedec 8,8gt/s, per poi passare alle ddr6.

Con i 3nm, hai densità sufficiente a poter realizzare un 16 core totale, ma il problema resta sempre la cache l3. Salvo non lanci le CPU già impilate.

Per farti un'esempio, 8 core zen4, hanno densità di 92mtx mm2 su 30mm2. 16 core zen4 per farceli stare su 30mm2, ti servirebbe 184mt xmm2 (densità da 3nm), e purtroppo la cache non viene dimezzata con i 3nm, quindi per passare a 64 dovresti allargare il CCD.

Ovviamente su zen4, ma con i prossimi i transistor saranno molti di più per core.

Quote:

Originariamente inviato da paolo.oliva2

Sugli APU AMD vedo una potenza Tops riferita all'NPU e poi "fino a" nell'utilizzo IA condiviso NPU/iGPU/X86... e il core C ci va a pennello, perchè aumenta il core-count favorevolmente rispetto all'are rispetto ai core P, aumenta la prestazione/efficienza...

Per me faranno una cippone L2/L3 stile IBM, nel centro, bello condiviso tra 1-8 Chiplet, con funzione IOD. Tanto si passa già da 12 chiplet per X96 (Epyc Zen4) a 6 chiplet per X192 (Epyc Zen5C).

|

Per AI, servono tensor core più che altro.