Quote:

Per quanto riguarda l' impatto su processori con grandi cache che vuoi consuderare nella diluizione dei transistor aggiunti per l'HT, devi considerare quanto è il costo di un core separato. Facciamo che la proporzione è 1/5 tra tutti i transistor cache comprese, quanto mi costa aggiungere un core?

Mettiamo che un core senza HT pesa 1/6. È equivalente a un aggiunta del 16%.

|

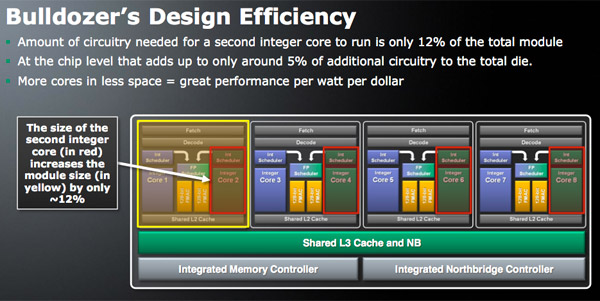

Ciao, il punto è che le percentuali che riporti sono spropositate per un core moderno. Se l'HT prendeva il 5% di area su un P4 senza L3/NB/PCIE, oggi impiega probabilmente meno del 2%. La duplicazione delle risorse avviene solamente per poche risorse del frontend, che a livello di area/transistor occupano (relativamente) pochissimo. Considera che un approccio CMP (che duplica tutto l'integer cluster e impone un frontend importante) l'incremento di area è il 12% per modulo e solo il 5% a livello di intero chip:

Va da sé che SMT2 (o HT), non duplicando nulla nel backend, impone overhead molto minori.

Quote:

Considerando che il contributo dell'HT diminuisce all'aumentare dell'IPC e che la maggior parte dei transistor sono spesi per aumentare quest' ultimo, ne deriva che man mano che migliori il core (spendendo transistor) l'HT peggiora.

Con l'aumento delle vie di esecuzione serve una struttura sempre più complessa per mantenere la funzionalità HT (raddoppio di molte strutture intermedie). Ne deriva quindi che il numero di transistor cresce più del necessario e già non sono pochi.

|

Non è l'aumento delle vie di esecuzione che limita l'uso dell'SMT, anzi. Guarda i Power7/8/9: i backend sono mastodontici, eppure beneficiano eccome dell'SMT. Il vantaggio dell'SMT diminuisce mano a mano che l'engine OoO diventa più complesso e riesce a estrarre un maggiore ILP su una finestra di istruzioni in-flight più ampia. Ma questo ha dei limiti, e un secondo thread di esecuzione è molto utile proprio su quei processori che hanno backend importanti. Se vogliamo il limite dell'HT di intel è proprio il contrario: fino a Skylake il backend era troppo stretto, mentre la logica OoO era molto evoluta. In altre parole, c'era poco da rosicare sul fondo del barile

Quote:

|

La soluzione è presto fatta: niente HT per un core più magro. ARM non ha mai sposato la filosofia SMT, e vediamo che se realizzati decentemente (e non solo per smartphone) le prestazioni ci sono senza necessità di SMT.

|

In realtà ARM ha lanciano un core basato su A65AE che supporta proprio l'SMT:

https://www.anandtech.com/show/13727...t-smt-cpu-core

I Cortex A510 supportano invece la modalità merged-cores che richiamano in modo abbastanza evidente (suppor con importanti differenze) l'approccio CMP di AMD:

https://www.anandtech.com/show/16693...0-cortexa510/4

Quote:

|

È la dimostrazione che l'SMT è giunto al capolinea, superato su desktop e su CPU per lavori altamente parallelizzati dove molto più core piccoli sono sempre meglio di meno core super pompati.

|

Vero: tanti piccoli cores hanno prestazioni aggregate maggiori di pochi core potenti, ma questo si sa da sempre. La vera novità è che le prestazioni dei "mid-cores" sono diventate sufficienti a non causare problemi di lentezza nel normale uso, dove la latenza gioca ancora un ruolo importante. Per tanti scenari d'uso, quindi, i "big cores" stanno semplicemente diventando superflui.

Quote:

|

Non mi meraviglierei se i futuri P-core aumentassero l'IPC togliendo l'SMT nel prossimo futuro risparmiando in transistor e quindi liberando spazio per più P-core stessi o più E-core.

|

Anche questo è possibile, ma penso per una diversa motivazione: il progressivo allontanamento delle architetture client da quelle server, con queste ultime che saranno le uniche a ricevere determinate features. Chiaramente poi bisogna attendere e vedere come andranno davvero le cose...

Ciao.