Traduzione dal giapponese all'italiano...

http://www.microsofttranslator.com/b...23_428720.html

Si capisce, alla buona:

- Uso di un tipo di flip flop per ridurre la potenza dissipata, il secondo dall'alto:

- Passaggio da celle 6T a 8T per le caches

- 20% di incremento di frequenza a parità di tutto (io avevo supposto 10-15% per il FO4, ma oltre al FO4 hanno cambiato Flip Flop e caches...)

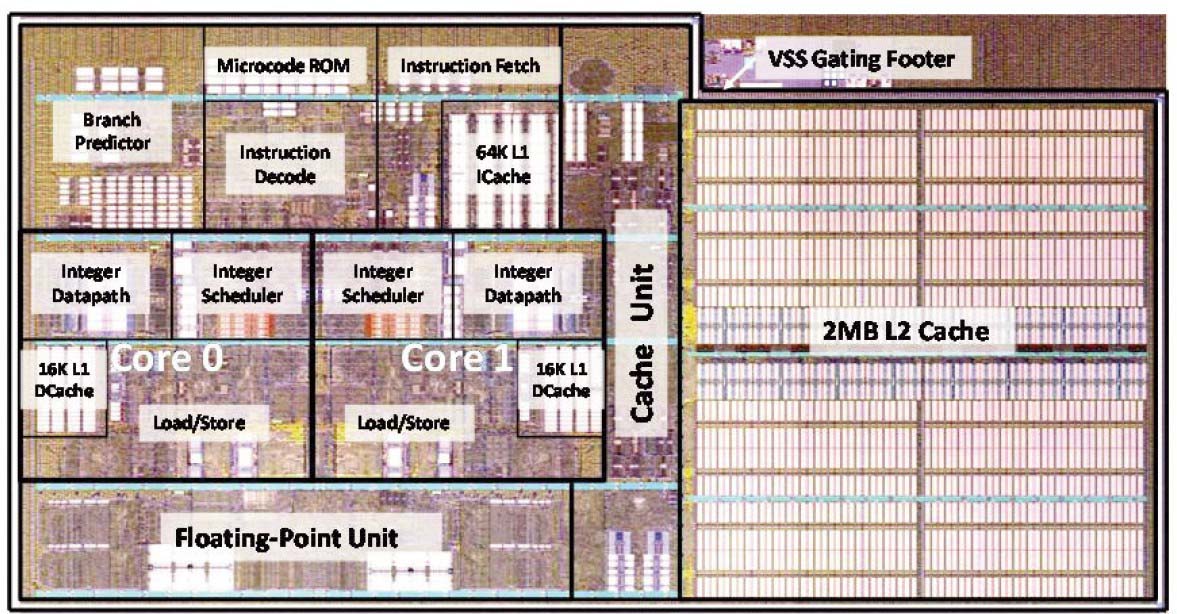

- Bonus: foto di un modulo...

Quindi abbiamo miglioramenti oltre quanto ipotizzavo io... Però la traduzione è confusa, può anche darsi che il 20% in frequenza sia dovuto al FO4, ai flip flop, alle caches, al clock gating e a tutte le tecniche di risparmio energetico... Se fosse così avremmo 20% per l'architettura e 40% per il processo... E siamo ancora più o meno con i conti che ho fatto sopra...