Intel Xeon 5500: architettura delle cpu Nehalem per server

Intel estende le novit‡ architetturali della famiglia Nehalem anche alla serie di processori Xeon, con le cpu 5500. Ben 17 versioni disponibili al lancio, con frequenze di clock, consumi e prezzi tali da soddisfare tutti i segmenti del mercato.

di Paolo Corsini pubblicato il 30 Marzo 2009 nel canale ProcessoriIntel

Gli elementi base delle cpu della famiglia Nehalem

Al pari di quanto osservato con la precedente generazione di architettura Intel, quella delle cpu Core 2, evidenziamo come le cpu Nehalem condividano una base tecnica comune indipendente dal tipo di finalit‡ di utilizzo tra sistemi server, desktop e notebook. Intel ha scelto di sviluppare un design unico che puntasse ad abbinare prestazioni velocistiche con consumi contenuti, segmentando in un secondo momento i processori in funzione dello specifico ambito di utilizzo.

Analizzando le caratteristiche tecniche delle cpu Nehalem a confronto con quelle della famiglia Core 2 appare evidente come il team di sviluppo abbia voluto implementare funzionalit‡ che portano i maggiori benefici prestazionali in ambito server, con un approccio che per molti versi possiamo considerare simile quanto a filosofia a quello svolto in passato da AMD con il debutto delle prime cpu della famiglia K8, modelli Opteron e Athlon 64. Questi gli elementi base che caratterizzano le cpu della famiglia Nehalem:

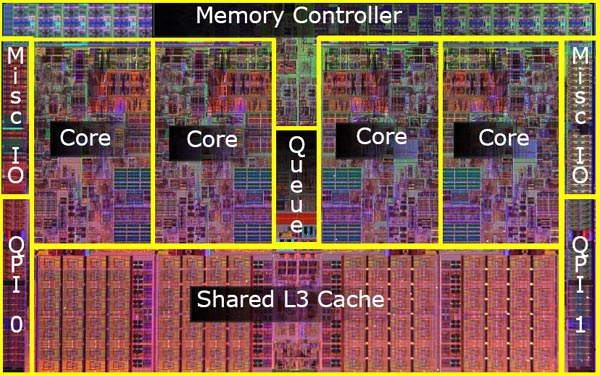

- architettura quad core di tipo nativo: Intel ha abbandonato l'approccio Multi Chip Package scegliendo quello che viene definito come design monolitico per le proprie cpu Nehalem. I 4 core, al pari delle soluzioni Phenom di AMD, sono tutti integrati nello stesso blocco di silicio e non ottenuti affiancando due die dual core sullo stesso package;

- memory controller DDR3 integrato nel processore: una novit‡ per i processori Intel, il memory controller integrato Ë da tempo presente sul mercato con le cpu AMD sin dalla famiglia K8, con il primo modello di cpu Opteron presentato nel mese di Aprile 2003;

- cache L3 integrata on die in tutti i processori, in quantitativo variabile che puÚ raggiunge gli 8 Mbytes in versioni quad core; parallelamente la cache L2, di tipo specifico per ogni core, Ë stata ridotta sensibilmente in dimensione rispetto a quanto implementato in precedenza con i processori della serie Core 2;

- ritorno della tecnologia Simultaneous Multi-Threading, meglio nota con il nome marketing di Hyper-Threading, grazie alla quale il sistema operativo riconosce il processore come dotato di un numeero di core logici doppio rispetto ai core fisicamente integrati. Questa tecnologia Ë stata introdotta in passato da Intel con alcune versioni di processore Pentium 4 ma non implementata nelle soluzioni Core 2 Duo e Core 2 Quad;

- nuovo set di istruzioni SSE 4.2, estensione delle istruzioni SSE4 introdotte per la prima volta da Intel con le cpu Core 2 basate su core Penryn;

- debutto della tecnologia QPI, Quick Path Interconnect, che sostituisce il front side bus nel collegamento tra processore, moduli memoria e in alcune versioni di cpu anche chipset.

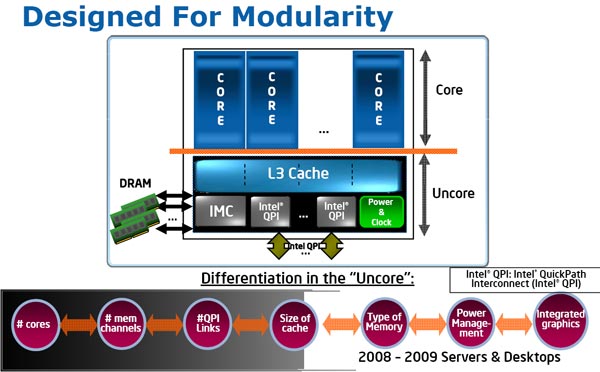

Le prime versioni di processore Nehalem con architettura quad core, le soluzioni della famiglia Core i7 e Xeon 5500, integrano 731 milioni di transistor costruiti utilizzando processo produttivo a 45 nanometri e integrando 8 Mbytes di cache L3. Successive evoluzioni di processore Nehalem, fermo restando il processo produttivo, sfrutteranno l'architettura modulare che Ë stata implementata nel progetto Nehalem in fase di design. Questi processori, infatti, possono essere facilmente modificati per implementare un differente numero di core, o integrare al proprio interno differenti tipologie di funzionalit‡ rispetto a quanto presentato nelle prime versioni al debutto.

La modularit‡ dell'architettura Nehalem puÚ essere facilmente spiegata riferendosi ai processori Nehalem-EX, soluzioni con 8 core fisici specificamente destinate all'utilizzo in sistemi server che debutteranno nel corso della seconda met‡ del 2009. Queste cpu implementano un design a 8 core di tipo nativo, quindi non con approccio Multi Chip Module, con una dotazione di cache L3 che dovrebbe essere pari a 24 Mbytes.

E' interessante evidenziare come con questa architettura di processori Intel di fatto abbia scelto non tanto di aumentare il numero di core, quanto di rendere ognuno di quelli presenti ancor pi˘ efficienti rispetto a quanto ottenuto con le soluzioni della famiglia Core 2. L'introduzione della tecnologia Hyper-Threading Ë una tecnica efficace per incrementare il parallelismo di esecuzione senza dover inserire nel die un numero elevato di transistor in pi˘, ma vedremo nelle pagine seguenti come Intel abbia operato con Nehalem da un lato affinando l'execution engine alla base delle cpu Core 2, dall'altra introducendo quelle novit‡ architetturali menzionate in precedenza che separano in modo chiaro e netto le cpu Nehalem da quelle di precedente generazione.

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone'

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone' Appian: non solo low code. La missione è líottimizzazione dei processi con l'IA

Appian: non solo low code. La missione è líottimizzazione dei processi con l'IA Lenovo ThinkVision 3D 27, la steroscopia senza occhialini

Lenovo ThinkVision 3D 27, la steroscopia senza occhialini  Arriva l'ok da Parlamento europeo sul diritto alla riparazione. Ecco cosa cambierà

Arriva l'ok da Parlamento europeo sul diritto alla riparazione. Ecco cosa cambierà RISC-V: l'uso dell'ISA open-source da parte della Cina preoccupa gli Stati Uniti

RISC-V: l'uso dell'ISA open-source da parte della Cina preoccupa gli Stati Uniti Amazon scatenata: iPad a 399Ä, airfryer 38Ä, smartphone, portatili e moltissimi articoli in svendita!

Amazon scatenata: iPad a 399Ä, airfryer 38Ä, smartphone, portatili e moltissimi articoli in svendita! SK hynix, costruzione della Fab M15X ai nastri di partenza: previsto boom delle memorie HBM

SK hynix, costruzione della Fab M15X ai nastri di partenza: previsto boom delle memorie HBM Oggi 459Ä per utenti Prime il portatile low cost con AMD Ryzen 7 5700U (8C/16T a 4,3GHz), 16GB RAM, SSD 512GB, Full HD!

Oggi 459Ä per utenti Prime il portatile low cost con AMD Ryzen 7 5700U (8C/16T a 4,3GHz), 16GB RAM, SSD 512GB, Full HD! Sta per succedere! La prima gara a guida autonoma sarà il 27 aprile: come vederla online

Sta per succedere! La prima gara a guida autonoma sarà il 27 aprile: come vederla online Parthenope: un nuovo RPG investigativo tutto italiano e ambientato a Napoli

Parthenope: un nuovo RPG investigativo tutto italiano e ambientato a Napoli Urbanista Malibu: ecco come va la cassa Bluetooth con ricarica solare

Urbanista Malibu: ecco come va la cassa Bluetooth con ricarica solare Gas Station Simulator è costato 110 mila euro e ha guadagnato più di 10 milioni su Steam

Gas Station Simulator è costato 110 mila euro e ha guadagnato più di 10 milioni su Steam AOC Graphic Pro U3, tre nuovi monitor per i professionisti creativi

AOC Graphic Pro U3, tre nuovi monitor per i professionisti creativi Wacom Movink: per la prima volta il display interattivo ha uno schermo OLED

Wacom Movink: per la prima volta il display interattivo ha uno schermo OLED HPE Aruba presenta i nuovi access point serie 730: oltre il Wi-Fi 7, arriva anche l'IoT

HPE Aruba presenta i nuovi access point serie 730: oltre il Wi-Fi 7, arriva anche l'IoT Lamborghini presenta Urus SE, prima versione ibrida plug-in del Super SUV

Lamborghini presenta Urus SE, prima versione ibrida plug-in del Super SUV