K8L e Quad Core: un poker da AMD

Nel corso del 2007 AMD presenterŕ la piů importante evoluzione della propria architettura di processore, sotto il nome di K8L. Varie innovazioni si abbineranno alla presenza di 4 core nello stesso package, interessando prima le soluzioni Opteron e poi quelle Athlon 64 e Turion 64. Ma K8L troverŕ spazio anche nei sistemi dual core, ancora in auge nei prossimi 2 anni.

di Paolo Corsini pubblicato il 11 Ottobre 2006 nel canale ProcessoriAMD

Le architetture Quad Core

Come evidenziato in precedenza, AMD introdurrŕ nel corso del 2007 le proprie architetture Quad Core; queste soluzioni adotteranno il Core noto con il nome in codice di K8L, che oltre alla presenza dei 4 core di processore implementerŕ varie innovazioni architetturali. Per utilizzare un'immagine, quindi, le prime cpu Quad Core di AMD non saranno una sorta di fusione tra due core Dual Core, come invece accadrŕ per le prime soluzioni Quad Core di Intel attese per il mese di novembre, ma di fatto un'architettura completamente nuova, anche se di fondo basata su quella delle soluzioni Athlon 64 e Opteron attualmente disponibili in commercio.

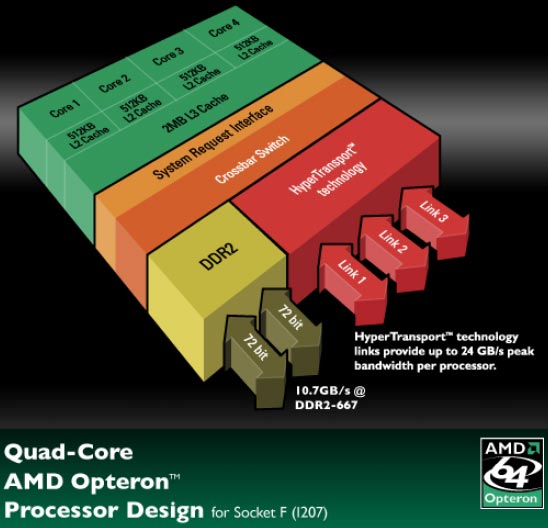

Alla base delle nuove cpu Quad Core troviamo, per le piattaforme Opteron, lo stesso Socket di connessione con la scheda madre utilizzato con le cpu Opteron Revision F, dotate di supporto alla memoria DDR2 e introdotte ufficialmente sul mercato dal produttore americano nel corso del mese di Agosto 2006. Se le cpu Opteron sono state le ultime a ricevere l'aggiornamento alla Revision F, che ha introdotto il controller memoria DDR2, queste saranno le prime ad adottare il nuovo Core K8L con architettura Quad Core. Il controller memoria rimane quello DDR-2 delle soluzioni Opteron, con una differenza data dall'utilizzare due controller separati da 72bit di ampiezza ciascuno (64bit dati e 8 bit per il controllo paritŕ) contro l'unico canale a 144bit (128bit dati e 16bit controllo) adottato attualmente: questo dovrebbe permetterne un migliore sfruttamento soprattutto quando vengono effettuate piccole ma frequenti richieste di dati.

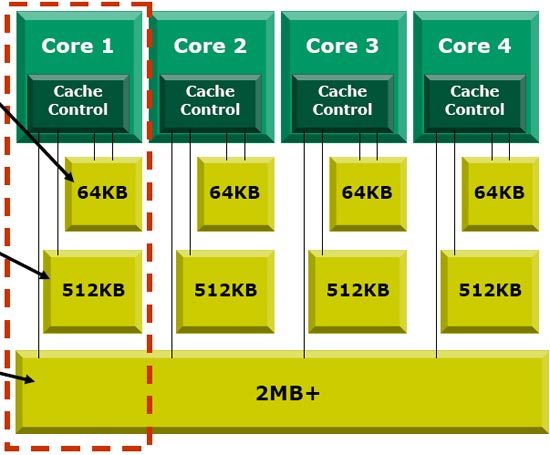

Per ciascun Core di processore continuerŕ ad essere presente una cache L1 da 128 Kbytes, divisa in due blocchi indipendenti da 64 Kbytes ciascuno per dati e istruzioni, affiancata da una cache L2 da 512 Kbytes, quantitativo equivalente a quello di olte soluzioni Athlon 64 sia single che Dual Core commercializzate da AMD e pari invece alla metŕ di quello di 1 Mbyte che viene fornito con i processori Opteron sia single che Dual Core in commercio. Le due cache sono di tipo esclusivo, caratteristica giŕ presente nelle precedenti versioni di processore Athlon 64 e Opteron: questo implica pertanto che i dati contenuti nela cache L1 non siano replicati in quella L2, e viceversa.

In aggiunta alle cache L1 ed L2 AMD ha integrato in queste architetture una cache di terzo livello, o L3, che verrŕ inizialmente proposta in quantitativo pari a 2 Mbytes ma che potrebbe venir ampliata in successive revision di processore, nel momento in cui saranno disponibili tecnologie produttive piů sofisticate di quella a 65 nanometri utilizzata per le soluzioni K8L.

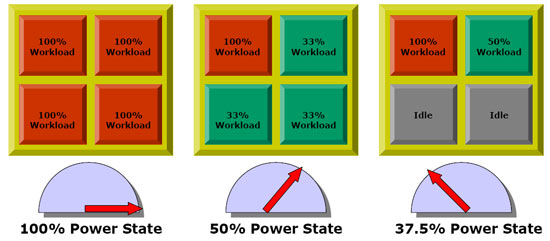

AMD ha inoltre svolto un notevole lavoro per ottimizzare il consumo delle nuove architetture Quad Core, dichiarando valori di TDP identici a quelli delle soluzioni Dual Core; per questo motivo non sarŕ necessario modificare i sistemi di raffreddamento e di alimentazione delle soluzioni server Opteron Socket 1207 pin attualmente in commercio per aggiornarle alle nuove soluzioni di processore Quad Core. Il sistema di risparmio energetico implementato nelle architetture Quad Core permette di gestire in modo individuale e indipendente per ciascun core la frequenza di funzionamento, ma non il suo voltaggio che rimarrŕ identico tra i vari core, a patto di utilizzare sul proprio sistema i driver PowerNow! corrispondenti che abilitano questa funzionalitŕ da lato sistema operativo

In aggiunta a questo, K8L integrerŕ una logica di gestione dell'alimentazione di processore e memory controller differenziata: per questo motivo, pertanto, cpu e controller memoria potranno ricevere voltaggi differenti in funzione del tipo di carico chiesto in un preciso istante, cosě da minimizzare il consumo complessivo.

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone'

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone' Appian: non solo low code. La missione è l’ottimizzazione dei processi con l'IA

Appian: non solo low code. La missione è l’ottimizzazione dei processi con l'IA Lenovo ThinkVision 3D 27, la steroscopia senza occhialini

Lenovo ThinkVision 3D 27, la steroscopia senza occhialini  Arriva l'ok da Parlamento europeo sul diritto alla riparazione. Ecco cosa cambierà

Arriva l'ok da Parlamento europeo sul diritto alla riparazione. Ecco cosa cambierà RISC-V: l'uso dell'ISA open-source da parte della Cina preoccupa gli Stati Uniti

RISC-V: l'uso dell'ISA open-source da parte della Cina preoccupa gli Stati Uniti Amazon scatenata: iPad a 399€, airfryer 38€, smartphone, portatili e moltissimi articoli in svendita!

Amazon scatenata: iPad a 399€, airfryer 38€, smartphone, portatili e moltissimi articoli in svendita! SK hynix, costruzione della Fab M15X ai nastri di partenza: previsto boom delle memorie HBM

SK hynix, costruzione della Fab M15X ai nastri di partenza: previsto boom delle memorie HBM Oggi 459€ per utenti Prime il portatile low cost con AMD Ryzen 7 5700U (8C/16T a 4,3GHz), 16GB RAM, SSD 512GB, Full HD!

Oggi 459€ per utenti Prime il portatile low cost con AMD Ryzen 7 5700U (8C/16T a 4,3GHz), 16GB RAM, SSD 512GB, Full HD! Sta per succedere! La prima gara a guida autonoma sarà il 27 aprile: come vederla online

Sta per succedere! La prima gara a guida autonoma sarà il 27 aprile: come vederla online Parthenope: un nuovo RPG investigativo tutto italiano e ambientato a Napoli

Parthenope: un nuovo RPG investigativo tutto italiano e ambientato a Napoli Urbanista Malibu: ecco come va la cassa Bluetooth con ricarica solare

Urbanista Malibu: ecco come va la cassa Bluetooth con ricarica solare Gas Station Simulator è costato 110 mila euro e ha guadagnato più di 10 milioni su Steam

Gas Station Simulator è costato 110 mila euro e ha guadagnato più di 10 milioni su Steam AOC Graphic Pro U3, tre nuovi monitor per i professionisti creativi

AOC Graphic Pro U3, tre nuovi monitor per i professionisti creativi Wacom Movink: per la prima volta il display interattivo ha uno schermo OLED

Wacom Movink: per la prima volta il display interattivo ha uno schermo OLED HPE Aruba presenta i nuovi access point serie 730: oltre il Wi-Fi 7, arriva anche l'IoT

HPE Aruba presenta i nuovi access point serie 730: oltre il Wi-Fi 7, arriva anche l'IoT Lamborghini presenta Urus SE, prima versione ibrida plug-in del Super SUV

Lamborghini presenta Urus SE, prima versione ibrida plug-in del Super SUV