Perchè integrare CPU e GPU in un unico elemento

Integrazione tra GPU e CPU: è questa la principale evoluzione tecnologica che AMD si aspetta di presentare al mercato nei prossimi anni. Il nome scelto per i prodotti che integreranno GPU e CPU è quello di Fusion, che ben simboleggia l'unione tra architetture sulla carta e di fatto molto differenti tra di loro. La risultante saranno una serie di prodotti sviluppati per svariati ambiti di impiego, nei quali quindi la combinazione tra parte CPU classica e parte GPU assumerà pesi differenti tra di loro.

Per quale motivo si vuole giungere a fornire soluzioni che integrino al proprio interno una GPU? La principale giustificazione è legata all'elevata potenza elaborativa di cui sono capaci le GPU, in termini di Gflops, rispetto a quanto accessibile con una CPU. Merito di questo risultato è l'innata capacità delle GPU di eseguire un gran numero di elaborazioni parallele, richieste per la generazione delle scene 3D. Sfruttando un'analogia, una CPU opera come un aereo da combattimento, estremamente veloce ma in grado di trasportare solo due persone contemporaneamente; una GPU è invece paragonabile ad un aereo di linea, meno veloce in assoluto ma capace di trasportare molte più persone e quindi di svolgere complessivamente più lavoro.

Le GPU hanno una potenza di elaborazione massima teorica estremamente elevata, sintetizzata dai Gflops che possono processare; si tratta tuttavia di una capacità per molti versi vincolata, che può essere sfruttata solo con quelle applicazioni che richiedono l'elaborazione di un elevato numero di dati in parallelo. Per questo motivo gli ambiti di utilizzo delle GPU in elaborazioni non grafiche di calcolo generale, o più semplicemente GP-GPU, sono limitati ad alcune tipologie di elaborazione; è evidente come nel corso dei prossimi anni gli sviluppatori software, grazie all'introduzione delle OpenCL e anche alla disponibilità di GPU sempre più complesse oltre che potenti e estremamente programmabili, potranno operare ad una nuova tipologia di software dove la GPU si prenda in carico i calcoli più pesanti in modo da eseguire operazioni in minor tempo possibile.

Un pò di storia

Il primo tentativo in assoluto fu la creazione di un Dual core nativo K10 senza cache L3 a 45nm SOI, il quale sarebbe stato accoppiato sullo stesso package una IGP della serie RV620 (cioè la stessa degli attuali chipset AMD 785G/880G) costruita a 55nm bulk; lo stile costruttivo era lo stesso dei processori Intel core Clarkdale.

Il progetto fu accantonato per problemi logistici legati alle differenti tecnologie costruttive dei due chip principali (CPU IBM SOI e GPU TSMC bulk); così il primo progetto Fusion fu cancellato ma AMD come eredità rilasciò sul mercato il K10 Dual core nativo con il nome di Athlon2 core Regor.

APU Llano: la prima APU AMD!

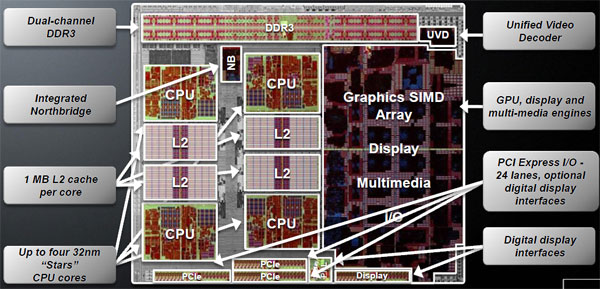

AMD passò quindi allo scenario più complesso cioè

un unico componente di silicio nel quale i transistor della parte CPU sono integrati con quelli della parte GPU e viceversa con tecnologia costruttiva a 32nm SOI.

APU (Accelerated Processing Unit)

Llano è composto da core X86 derivanti dall'architettura

K10 e una GPU

DX11 costruiti e prodotti entrambi a 32nm con tecnologia SOI provenienti da

Globalfoundries; questa soluzione rappresenta la prima GPU di origine ATI costruita con la tecnologia SOI di IBM.

Ciascuno dei core x86 implementati nella APU avrà una superficie complessive molto contenuta, pari a 9,69 millimetri quadrati, per un totale di poco più di

35 milioni di transistor; da questo conteggio è esclusa

la cache L2 da 1 Mbyte, indipendente per ciascuno dei core. AMD dichiara un range di consumo variabile da un minimo di

2,5 Watt sino a 25 Watt per ciascuno dei core: questo significa, che sarà possibile vedere sul mercato versioni di APU con valori di TDP molto diversi tra loro.

Grazie a alcune precise strategie di design, la APU introduce la modalità

Package C6, la quale permette di diminuire l'alimentazione sull'intera struttura compresa la GPU e modulo UVD di terza generazione.

L'introduzione di tale modalità permette a ogni singolo core X86 di venir spento, anche il core grafico può essere completamente spento, mentre il consumo del controller RAM per la componente grafica può essere gestito dinamicamente.

Per ottenere tutto questo AMD ha implementato una singola linea di alimentazione VDDNB condivisa tra GPU, UVD, controller memoria grafico e northbridge; con questa è possibile gestire dinamicamente sia la tensione sia la frequenza di clock, con il primo elemento che viene selezionato in funzione dello stato nel quale si trovano questi componenti.

Ulteriore ottimizzazione al consumo dell'intero sistema è implementata con la tecnologia

adaptive backlight modulation; in pratica l'immagine riprodotta a schermo viene analizzata in modo da ridurre gradualmente l'intensità della backlight incrementando la luminosità dei pixel, riducendo il consumo complessivo dello schermo senza che questo porti ad una variazione percepibile da parte dell'utente della luminosità complessiva dell'immagine a video.

A inizio Ottobre 2012 AMD utilizzerà l'architettura

Bulldozer di seconda generazione per le future soluzioni APU denominate

"Trinity".

APU Llano serie A8, A6 e A4

AMD ha presentato tre tipologie di APU cioè la serie

A8 e la serie

A6, entrambi con 4 core e la serie A4 composta da 2 core tutti derivanti dall'architettura

K10, opportunamente modificata per il processo produttiva a

32nm SOI; ogni core avrà una cache L2 da

1MB mentre sarà completamente

assente la cache L3.

Ciascuna APU viene proposta con due TDP differenti, con un massimo di

100W e un minimo di

65W.

A differenziare le tre serie sono il numero di

Stream Processors della

GPU DX11, infatti la serie A8 ha una GPU denominata

HD6550D con

400SP (80SP 5 SIMPs VLIW-5 20 Texture Unit 8 ROP) e una frequenza di

600Mhz, mentre la serie A6 ha una GPU denominata

HD6530D con

320SP (80SP 4 SIMPs VLIW-5 16 Texture Unit 8 ROP) e una frequenza di

443Mhz; per la serie A4 la GPU prende il nome di

HD6410D con

160SP e una frequenza di

443Mhz.

Per quanto riguarda la tecnologia

AMD Turbo Core 2.0 sui core X86 alcuni modelli implementano supporto a tale tecnologia, mentre sarà assente in altri modelli con frequenze di clock di default più elevate.

Il controller RAM può gestire memorie

DDR3 in Dual channel con frequenza

1333/1600/1866Mhz per la serie A8/A6, mentre per la serie A4 la gestione massima si ferma alla frequenza di

1600Mhz.

Piattaforma AMD "Linx" socket FM1

AMD per le APU Llano ha presentato la piattaforma

"Linx" composta dal

socket FM1 e non compatibile con le CPU di precedente generazione.

La differenza sostanziale è la mancanza del classico northbridge o chipset, questo perchè Llano integra già un chipset all'interno del DIE.

La novità è che sono stati immessi due nuovi southgbridge modelli

A75 e

A55.

A75 introduce, oltre le 6 porte

SATA3 già viste sui modelli SB950 (nuovo algoritmo),

4 porte USB 3.0 gestite direttamente dal southgridge; il modello A55 invece è provvisto di qualsiasi porta USB 3.0 interna e può gestire "solo" 6 porte

SATA2.

APU Trinity: La seconda generazione delle APU AMD

A più di un anno di distanza AMD presenta l'evoluzione delle APU Llano denominata

Trinity.

Questa APU ha

uno o due moduli core X86 (2 e 4 core)

con architettura Piledriver costruiti con il processo produttivo a

32nm SOI, la cache L2 dovrebbe essere da

2MB per modulo.;

La GPU DX11 sarà aggiornata all'architettura

VLIW 4-way utilizzata per le soluzioni

Cayman (serie HD6900).

Architettura "Piledriver"

Piledriver rappresenta un evoluzione dell'architettura a moduli denominata "Bulldozer", il design di base con 2 core x86 in un modulo, le due unità di calcolo integer accompagnato da una in virgola mobile con due moduli a 128bit di precisione,

rimane invariata compresa una cache L2 dedicata da 2/1MB (dipende dai modelli); come nella versione precedente manca una cache L3 presente invece nelle CPU serie FX.

Le novità dei core Piledriver sono varie ottimizzazioni rispetto a quanto adottato in Bulldozer tra qui le nuove istruzioni

ISA, FMA3 (inclusa una fused multiply-add) e

F16C(floating point 16-bit convert), il miglioramento dell'unità di branch prediction

suddiviso in una struttura a due livelli, una rinnovata efficienza della

cache L2 con particolare cura

sulle latenze, un ingrandimento del

istruction window e implememtazione un miglior

hardware prefetch.

La

L1 TLB (Translation Look-aside Buffer), è stata incrementata di dimensione rispetto all'architettura Bulldozer, infine è presente una più elevata efficienza complessiva dei core grazie ad miglioramenti allo

scheduler integer e al calcolo in

virgola mobile.

GPU con architettura VLIW4

Le APU Trinity avranno un evoluzione anche nella GPU integrata la quale avrà un architettura VLIW4 cioè la stessa di base per le soluzioni Radeon HD6900/6800; le soluzioni Llano montato una GPU con architettura

VLIW5.

In linea generale WLIW4 offre prestazioni per mm² più elevate, un flow control migliorato e risultati di calcolo della GPU superiori rispetto a WLIW5; ci sono anche miglioramenti nel tassellatore hardware, gestione dei thread più efficiente e supporto al buffering.

La GPU più potente di Trinity (modelli A10) nome in codice "Devastator" ha 4 ALU per thread processor per un totale 384 ALU e 24 unità texture in totale, 6 engine SIMD ognuno con 4 unità texturee 16 thread processors; infine AMD ha inserito il VCE (Video Codec Engine) tecnologia introdotta con la serie HD7000 per la codifica in hardware H.264.

Novità anche sul fronte Northbridge (UNB) completamente ridisegnato dove ora i core X86 e GPU condividono lo stesso componente per lo scambio molto più efficiente della memoria RAM, ai sottosistemi I/O.

Serie A10, A8, A6 e Athlon2 700

Con Trinity AMD introduce la serie

A10 top level di questa categoria di APU.

I modelli saranno composti da 2 moduli/

4 core X86 Piledriver, GPU

VLIW4 HD7660D con

384SP e frequenza di

800Mhz; alcuni modelli denominati

K avranno il moltiplicatore sbloccato verso l'alto e il

TDP può variare tra i

100W e i

65W.

La serie

A8 sarà composta da 2 moduli/

4 core X86 Piledriver, GPU

VLIW4 HD7560D con

256SP e una frequenza

760Mhz; anche in questo caso alcuni modelli denominati

K avranno il moltiplicatore sbloccato verso l'alto e un

TDP che può variare tra i

100W e i

65W.

La serie

A6 sarà composta da 1 modulo/

2 core X86 Piledriver GPU

VLIW4 HD7540D con

192SP e una frequenza

760Mhz; sembra che questa serie sia destinata solo alle versioni

K dual core ovvero con il moltiplicatore sbloccato verso l'alto, mentre il

TDP sarà di

65W.

La serie

A4 sarà composta da 1 modulo/

2 core X86 Piledriver GPU

VLIW4 HD7480D con

128SP e una frequenza

724Mhz; non ci saranno versioni K e il

TPD sarà di

65W.

Per finire la serie Athlon2 700 saranno composte da APU Trinity con la

GPU integrata completamente spenta, quindi anche se basati sul socket FM2 si dovrà montare

per forza una GPU esterna; alcuni di questi modelli saranno in versione

K e il

TDP varia tra i

100W e i

65W.

Infine ci sarà anche la serie Athlon2

300 in versione Dual core derivante dalla serie A4.

Tutti modelli APU decritti avranno il

Turbo Core 3.0, mentre la gestione delle DDR3 sarà alla frequenza di

1333/1600/1866Mhz tranne per il modelli

A4/Athlon2 300 dove la frequenza massima si ferma alla frequenza di

1600Mhz...

Turbo Core 3.0

AMD ha introdotto nelle soluzioni Trinity il Turbo Core di terza generazione il quale ora può intervenire, oltre che sui core X86, anche sulla frequenza della GPU a seconda del carico di lavoro.

Il funzionamento e la gestione delle frequenze è controllato da una sorta di power monitor disponibile su ogni modulo X86 e sulla GPU ed è direttamente dipendente dal TDP massimo e dal consumo della APU stessa.

AMD ha reso questo turbo

bidirezionale in modo da fruttare al massimo le variazione di frequenza (impostate a 100Mhz alla volta) a seconda del tipo di carico di lavoro...

Per fare un esempio se i calcoli sono concentrati sulla GPU la frequenza del turbo si concentra su questa unità, oppure se il calcolo è in uso su programmi prettamente single thread il turbo alzerà la frequenza del singolo modulo sotto carico.

Socket FM2 per la piattaforma Virgo

Per trinity AMD ha presentato una nuova piattaforma chiamata

"Virgo" bastata sul socket chiamato

FM2 il quale

prenderà il posto del primo socket FM1 presentato con l'uscita di Llano;

diciamo subito che i due socket sono incompatibili meccanicamente quindi le soluzioni Trinity non possono essere montate su schede per le APU Llano e viceversa.

Con questa nuova piattaforma AMD ha presentato il nuovo chipset FCH

A85X con ben

8 porte SATA3 e la gestione di

4 porte USB 3.0; vengono mantenuti anche i chipset

A75 e

A55 visti per la prima volta sulla precedente piattaforma Linx.

Architettura "Steamroller"

Con questa evoluzione dell'architettura a moduli, AMD punta a migliorare le performance a singolo thread grazie all'integrazione di una unità di

decode specifica per ognuna delle due pipeline integer integrate in ogni modulo; ricordo che l'architettura Bulldozer/Piledriver prevede una sola unità di Decode unificata tra le due unità integer; altra novità è l'aumento della velocità e dimensione della cache L1.

Con Steamroller AMD passerà da un processo produttivo

32nm SOI ad un processo produttivo a

28nm BULK proveniente sempre da Global Foundries; con questo atto AMD chiuderà l'epoca della tecnologia

IBM SOI introdotta con i primi

K8 a 130nm.

AMD Kaveri

Kaveri rappresenta la nuova generazione di APU di AMD e succede direttamente a Trinity/Richland; saranno disponibili modelli sia nel segmento desktop che mobile, con modelli che copriranno un TDP che varia dai 15W a 95 W.

Con questo modello AMD introduce delle importanti tecnologie:

HSA (Heterogeneous System Architecture)

IN AGGIORNAMENTO.....